鲁华祥研究员在2019北京智源大会介绍类脑芯片技术发展

时间:2019-10-3110月31日,由北京智源人工智能研究院主办的2019北京智源大会在京举办。在下午的智能体系架构与芯片专题论坛中,清华大学教授、类脑计算研究中心主任施路平,北京大学教授、智源研究员蔡一茂,中科院半导体所研究员、智源研究员鲁华祥,分别分享了关于类脑神经网络技术及芯片的现状、挑战及研发进展。

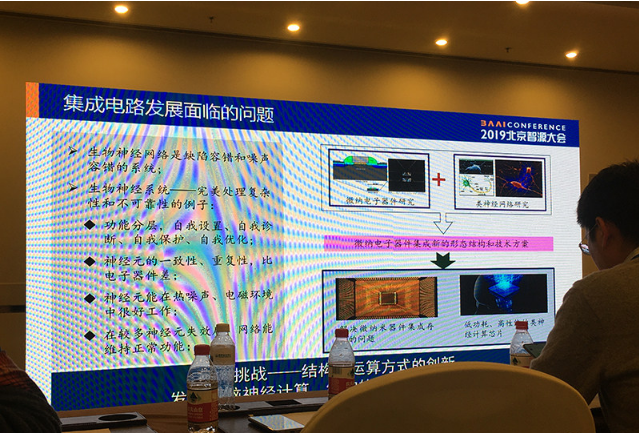

鲁华祥谈到,信息处理技术发展面临性能、能耗、可靠性、容错性等方面的问题。应对这些挑战,创新芯片结构及运算方式应运而生,芯片成为AI技术发展的核心推动力。与此同时,集成电路发展也面临着摩尔定律和微纳电子器件瓶颈所带来的的问题。新型纳米电子器件研究也在持续推进,半导体所利用的Si基或GaAs、InP基III-V超晶格量子阱材料,发展了多种纳米电子器件。而生物神经网络是缺陷容错和噪声容错的系统,这带来一种新的思路,将微纳电子器件研究与类神经网络研究相结合,集成新形态结构的芯片。

目前,类脑神经计算在国外用以解决下一代信息处理问题,以更低的功率开创全新计算机应用。欧盟、美国、日本、澳大利亚、加拿大、韩国均提出脑计划。“中国脑计划”是我国六个长期科学项目之一,分为脑科学和类脑科学两个部分,主要有两个研究方向,一是以脑疾病为导向的脑科学研究,二是以建立和发展AI技术为导向的类脑研究。类脑神经计算目前有两种主流的实现路径,一是以谷歌TPU为代表的功能模拟实现,二是以神经拟态芯片为代表的结构模拟实现。

鲁华祥还介绍了半导体所类脑神经计算、芯片的发展状况。半导体所借鉴人脑的信息处理机制进行类脑神经计算的算法和芯片研发,聚焦于“多权值”神经元模型和电路实现、串并行计算架构、局部字域结构、分布式异步控制技术、神经元集群架构设计等芯片关键技术。芯片方面,半导体所已研发出CASSANN系列类脑神经计算芯片,采用40nm CMOS工艺,集成16个神经元集群,4000万门、1亿个左右的晶体管,芯片内含65536个神经元,200万神经突触,每秒358亿次神经突触连接。半导体所也研发了基于CASSANN-X的类脑神经计算系统,用以解决复杂最优化问题。其成果已经应用在智能电网监测等“不确定、非完整信息”问题。

未来,半导体所将进一步研究三个方向,一是不精确、非完整信息的类神经计算技术和系统,二是高性价比的类神经计算芯片、系统和设计技术,三是缺陷容错和噪声容错的电路集成技术。