# Readout Electronics for Infrared Sensors

John L. Vampola Santa Barbara Research Center Goleta, California

# CONTENTS

| 5.1    | Introd  | uction                                                |

|--------|---------|-------------------------------------------------------|

| 5.2    | MOSF    | ET Primer                                             |

| 5.3    |         | stor Noise                                            |

| 5.4    |         | Performance Drivers                                   |

| 5.5    | ROIC    | Preamplifier Overview                                 |

|        | 5.5.1   | ROIC Preamplifier Signal-to-Noise Ratio               |

|        | 5.5.2   | System Sensitivity Flowdown                           |

| 5.6    | Reado   | ut Preamplifiers                                      |

|        | 5.6.1   | Analysis of the Resistor Transimpedance Amplifier 303 |

|        | 5.6.2   | Reset Integrators and Sampled Readout Circuits 306    |

|        | 5.6.3   | Self-Integrating Readout                              |

|        | 5.6.4   | Source Follower per Detector Readout                  |

|        | 5.6.5   | Capacitor Feedback Transimpedance Amplifier 316       |

|        | 5.6.6   | Injection Circuits                                    |

|        | 5.6.7   | Gate Modulation Circuits                              |

| 5.7    | Signal  | Processing                                            |

|        | 5.7.1   | Sample and Hold                                       |

|        | 5.7.2   | Correlated Double Sampling (CDS)                      |

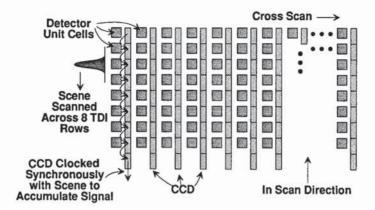

|        | 5.7.3   | Time-Delay Integration                                |

| 5.8    | Data N  | Multiplexers 329                                      |

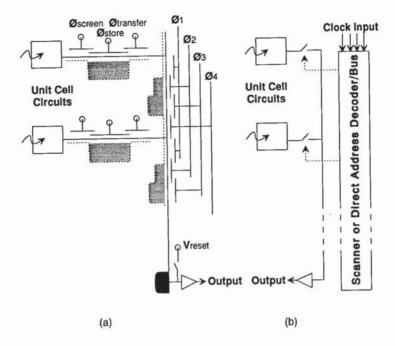

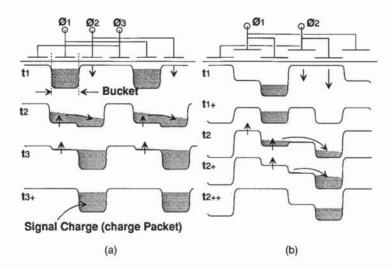

|        | 5.8.1   | CCD Multiplexers                                      |

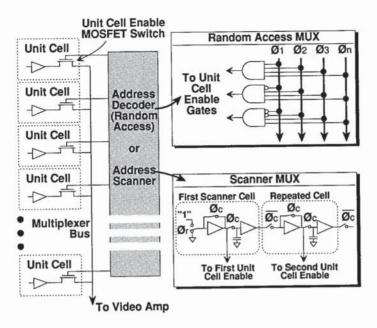

|        | 5.8.2   | Direct Address and Scanning Multiplexers              |

| 5.9    | Outpu   | t Video Amplifiers                                    |

| 5.10   | Power   | Dissipation                                           |

| 5.11   | Dynan   | nic Range 337                                         |

| 5.12   | Crosst  | alk and Frequency Response                            |

| 5.13   | Design  | Methodology                                           |

| Refere | ences . |                                                       |

| Biblio | graphy  | 340                                                   |

|        |         |                                                       |

#### 5.1 INTRODUCTION

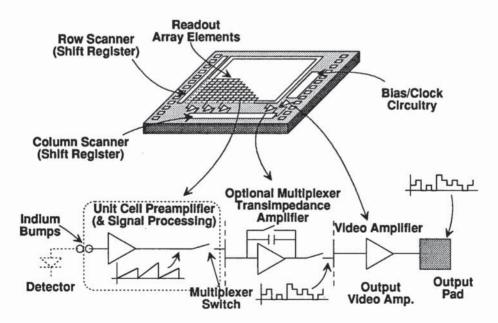

The readout integrated circuit (ROIC) is a highly integrated set of focal plane electronic functions combined into a single semiconductor chip. Its primary function is to provide infrared detector signal conversion and amplification, along with time multiplexing of data from many detectors to just a minimum number of outputs. ROICs can contain tens to hundreds of thousands of individual unit cells, each with critical detector amplifiers and multiplexer switches, as shown in Fig. 5.1. ROICs are normally processed using conventional silicon integrated circuit technology. They are most often implemented in complementary metal oxide semiconductor (CMOS) technology, allowing for higher resolution and greater sensitivity in today's sensors.

This chapter covers each of the ROIC functions shown in Fig. 5.1, including preamplifier, signal processor, multiplexer, and video amplifier sections. These functions are addressed in terms of major design drivers such as noise, dynamic range, and power. Since the signal-to-noise ratio (SNR) is the major driver in most sensor designs, each of the circuits is detailed in this context. The simplest circuits are introduced first to provide the basis for more advanced circuits. The resistor transimpedance amplifier (RTIA), which is most common in discrete configurations but also utilized in ROIC configurations, will be addressed initially to introduce many of the basic signal and noise concepts required for analysis of other preamplifier circuits in subsequent sections.

Fig. 5.1 The readout integrated circuit combines detector signal amplification, data multiplexing, and video output buffering of the infrared signal into a single chip. Shown is an example of a staring two-dimensional array.

High-impedance detectors, such as photovoltaics, extrinsic silicon, platinum silicide, and many photoconductors, are extremely sensitive to electromagnetic interference (EMI). A robust sensor design reduces EMI by locating the preamplifier as close as possible to the detector. Through the 1970s, preamplifiers were built up from discrete resistors, capacitors, and transistors into hybrids, which could be placed within inches of the detector. In the most sensitive applications, the front-end of the preamplifier, usually comprised of field effect transistors (FETs) and feedback resistors, was physically placed next to the detectors on the cold focal plane. Since a great amount of real estate would be required for such circuits, discrete amplifier designs put severe limitations on the number of detector channels that could be implemented in a given optical field of view.

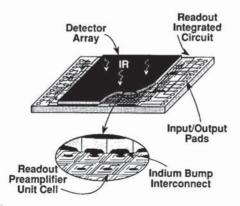

The first integrated approaches to addressing both high-density scanning arrays and two-dimensional focal planes were designed in the 1970s. Visible sensors, the ancestors of today's camcorder focal planes, were demonstrated utilizing a single silicon chip composed of charge-coupled devices (CCDs) that served as both sensor and multiplexer. The advent of indium bump interconnect technology, whereby matching sets of small indium bumps are formed on the detector and the CCD, provided the mechanism for connecting a large array to its readout, forming a sensor chip assembly (SCA) as shown in Fig. 5.2. Because of this history, sensor users often refer to all ROICs as multiplexers or CCDs even though CCD devices may not be employed.

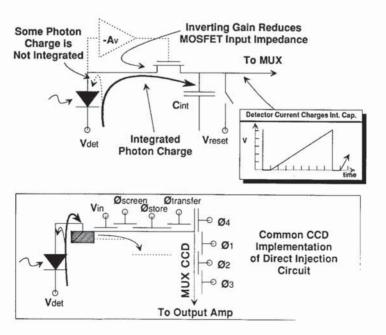

CCDs commonly utilize direct injection (DI) or gate modulation preamplifiers to buffer and accumulate the photon-induced current over a frame of scene data. These simple preamplifier types are covered in detail later in this chapter. Through the 1980s, as detector and integrated circuit densities increased, more elegant preamplifiers, as well as multiplexers and video drivers, were incorporated into the ROIC. These newer circuits expanded the use of SCAs to a broader set of applications by providing higher SNR, greater bandwidth, and better linearity. In addition to optimizing basic SCA functions,

Fig. 5.2 The readout integrated circuit mates with the detector array via indium bumps to form the sensor chip assembly capable of integrating hundreds to millions of elements onto a single assembly.

many other signal processing functions have also been integrated into the SCA, such as detector frame store and circuits that eliminate amplifier drift.

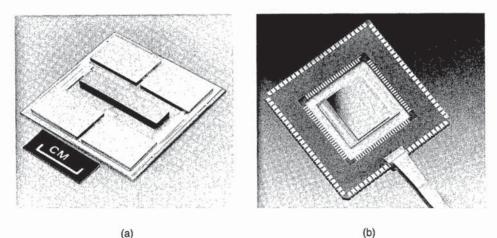

The ROIC, together with the detector, can be assembled to form various SCA configurations. The most common infrared configurations are the direct and the indirect hybrid SCAs of Fig. 5.3. A third type, the monolithic SCA configuration, is common in visible applications.

The direct hybrid SCA approach is common in high-density staring and scanning applications, which provide sufficient unit cell area under the detector element to accommodate a readout preamplifier and its associated circuitry. The direct hybrid SCA has fewer parts than the indirect and is therefore generally more producible.

Indirect hybrid SCAs can include one or more detector arrays fanned out to one or more ROICs via a single fanout board. Larger, more elaborate preamplifiers and signal processing electronics can be fabricated in the larger unit cells of indirect readouts, since the circuit area is no longer constrained to the real estate available under the detector element. The indirect hybrid can also reduce the stress caused by thermal mismatch between the detector and ROIC materials, thereby increasing the thermal cycle life of large SCAs.

A variation of the direct hybrid SCA design is the siderider SCA. This type of SCA includes additional signal processing circuitry, such as time delay integration (TDI), in the area of the ROIC adjacent to the detector array. The preamplifier signal, originating under each of the detector elements, is enabled to this siderider area of the ROIC for additional signal processing prior to being transmitted off the focal plane.

The monolithic device has both the detector and readout circuitry fabricated into a single semiconductor material. An example of a silicon monolithic device is the commercial camcorder SCA, which has the readout fabricated in the silicon adjacent to each of the detector elements. In this case the detector optical area is reduced to accommodate the readout circuitry, resulting in a low de-

Fig. 5.3 (a) The 960 × 4 element detector with four readouts mounted on a motherboard is an example of an indirect scanning SCA. (Courtesy of DARPA) (b) The  $640 \times 480$  element detector array coupled directly to the readout is an example of a staring direct hybrid SCA. (Courtesy of Santa Barbara Research Center)

tector (or optical) fill factor. Applications of the monolithic approach are also found in shorter wavelength infrared detector material, which utilizes CCD and FET devices.<sup>1</sup>

Common readout integrated circuit symbols, nomenclature, and units are given in Table 5.1.

#### 5.2 MOSFET PRIMER

Although discrete preamplifiers can be designed with bipolar junction transistor (BJT) or junction field effect transistor (JFET) technology, integrated circuit forms of the preamplifier are most commonly fabricated in silicon CMOS technology because of the operating temperature range, power, and noise characteristics of the metal oxide semiconductor FET (MOSFET). Silicon CMOS devices can be designed<sup>2</sup> to operate from room temperature to below 10 K. This MOSFET primer is meant as an introduction only. Detailed explanations of semiconductor physics and MOSFET action are available through many sources.<sup>3,4</sup> Liu and Nagel<sup>5</sup> treat the modeling of MOSFETs.

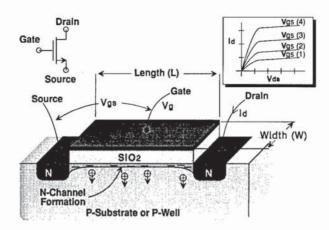

The N-channel MOSFET, shown in Fig. 5.4, is composed of n-implanted drain and source regions isolated from each other by the p-doped silicon substrate, or P-well. A gate, usually composed of polysilicon, lies above a thin dielectric layer (usually  $\mathrm{SiO}_2$ ) on the semiconductor surface between the two diffusions. In the simplest transistor action, a positive gate-to-source voltage  $V_{gs}$  induces a field in the surface region of the semiconductor. If the gate voltage is above a specific threshold  $V_t$ , the resulting field repels majority mobile carriers (holes) and attracts electrons, forming a very thin inversion region, or n-channel, at the surface of the semiconductor. The n-channel then provides a current path between the source and drain. The P-channel MOSFET is the same as the N-channel device but it utilizes opposite doping and voltages.

A sample plot of the drain current versus drain voltage at several gate voltages is shown in Fig. 5.4. Higher gate voltages increase the density of electrons at the surface and thus increase the conductance of the channel between source and drain diffusions. This action is useful in ROICs, because MOSFETs can be utilized as switches for multiplexing signals and resetting integration capacitors. MOSFETs are dimensioned according to the width W and length L of the channel. A short channel length will result in a desirable lower "on" resistance. Lower "on" resistance also can be achieved by either connecting two switches in parallel or by simply increasing the channel width of a single device. When the switch is on, the voltage between the source and drain is very small, and the transistor acts as a voltage-dependent resistor:

$$I_d \text{ (linear)} \approx \frac{W}{L} \mu_n C_0 (V_{gs} - V_t) V_{ds} \quad [A] ,$$

(5.1)

where  $\mu_n$  is the minority carrier mobility (electron in this case),  $C_0$  is the gate capacitance per unit area,  $V_{gs}$  is the gate-to-source voltage,  $V_t$  is the threshold voltage, and  $V_{ds}$  is the drain-to-source voltage. The "on" resistance of the MOSFET in the linear region of operation is approximately

Table 5.1 Common Readout Symbols, Nomenclature, and Units

| Symbol                     | Description                                                    | Units                              |

|----------------------------|----------------------------------------------------------------|------------------------------------|

| $A_{ m opt}$               | Optical area of the detector                                   | cm <sup>2</sup>                    |

| $A_{sf}$                   | Source follower buffer gain                                    | V/V                                |

| $A_v$                      | Amplifier or buffer voltage gain                               | V/V                                |

| $C_{ m clamp}$             | Clamp storage capacitor                                        | F                                  |

| $C_{fb}$                   | Feedback capacitance                                           | F                                  |

| $C_0$                      | MOSFET gate capacitance per unit area                          | F/cm <sup>2</sup>                  |

| $C_{sh}$                   | Sample and hold storage capacitor                              | F                                  |

| $C_{st}$ , $C_{\rm stray}$ | Stray node capacitance                                         | F                                  |

| D*                         | Normalized detector signal to noise                            | Jones                              |

| $\Delta f$                 | Power bandwidth                                                | Hz                                 |

| ein                        | Input referred noise voltage                                   | volts rms                          |

| $e_n$                      | Input noise voltage                                            | volts rms                          |

| f                          | Frequency                                                      | F                                  |

| $g_m$                      | MOSFET drain current to gate-source voltage (transconductance) | mohs                               |

| idet                       | Detector noise current                                         | amps rms                           |

| in                         | Input referred noise current                                   | amps rms                           |

| int                        | Integrated photon-induced current                              | A                                  |

| i <sub>n</sub>             | Input noise current                                            | amps rms                           |

| $I_d$                      | MOSFET drain current                                           | A                                  |

| dark                       | Detector dark current                                          | A                                  |

| k                          | Boltzmann constant                                             | J/K                                |

| L                          | MOSFET channel length                                          | cm                                 |

| m                          | MOSFET subthreshold factor                                     | _                                  |

| NEC                        | Noise equivalent charge                                        | e-                                 |

| NEI                        | noise equivalent irradiance                                    | ph/cm <sup>2</sup> s <sup>-1</sup> |

| q                          | Electron charge                                                | C                                  |

| $q_c$                      | Noise charge on a capacitor                                    | e rms                              |

| rdet                       | Detector resistance                                            | Ω                                  |

| rin                        | Amplifier input resistance                                     | Ω                                  |

| $r_s$                      | Source (detector resistance)                                   | Ω                                  |

| R                          | Resistor                                                       | Ω                                  |

| $R_{fb}$                   | Feedback resistance                                            | Ω                                  |

| Ron                        | MOSFET "on" resistance                                         | Ω                                  |

| $R_0$                      | Zero bias detector resistance                                  | Ω                                  |

| frame                      | Period from frame to frame                                     | s                                  |

| int                        | Signal current integration time                                | s                                  |

| T                          | temperature                                                    | K                                  |

| $T_{ m det}$               | Detector temperature                                           | K                                  |

| $T_{Rfb}$                  | Feedback resistor temperature                                  | K                                  |

| V <sub>c</sub>             | Noise voltage on a capacitor                                   | volts rms                          |

| Pout                       | Output referred noise voltage                                  | volts rms                          |

| $V_{ds}$                   | MOSFET drain-to-source voltage                                 | v                                  |

| $V_{gs}$                   | MOSFET gate-to-source voltage                                  | v                                  |

| $V_t$                      | MOSFET turn on threshold voltage                               | v                                  |

| W                          | MOSFET channel width                                           | cm                                 |

| Z                          | Charge to voltage gain                                         | V/C                                |

| Greek:                     | 1000 Tu 00 1/10 Tu Tu Tu Tu Tu                                 | 1407 F                             |

| η                          | Photon to electron conversion efficiency                       | e <sup>-</sup> /ph                 |

| η <sub>ie</sub>            | Photon current injection efficiency                            | A/A                                |

| $\mu_n$                    | N-channel MOSFET minority carrier mobility                     | $cm^2/V s^{-1}$                    |

| 1/f noise                  | Noise of 1/f power spectral density characteristics (drift)    | J                                  |

Fig. 5.4 Most ROICs utilize the MOSFET to perform as both amplifier and switch. Drain current is controlled by the gate-to-source voltage.

$$R_{\rm on} \, ({\rm linear}) \approx \frac{L}{W \mu^n C^0 (V^{gs} - V^t)} \, \left[ \Omega \right] \, .$$

(5.2)

This simple explanation of transistor action is adequate, in the case of the switch, where the voltage between source and drain is driven to zero when the switch is on. When the drain-to-source voltage is increased, however, the drain current eventually saturates and no longer increases with the drain voltage. The transistor is then said to be in *saturation*, which is the case with most analog MOSFET amplifiers. The drain saturation current can be approximated as

$$I_d \text{ (sat)} = \frac{W}{2L} \mu_n C_0 (V_{gs} - V_t)^2 \text{ [A]} .$$

(5.3)

Analogous to the "on" resistance of a switch, the most important parameter describing the action of the MOSFET amplifier is its transconductance  $g_m$ , which is defined as the change in drain current for a given change in gate-to-source voltage

$$g_m \text{ (sat)} \approx \frac{W}{L} \mu_n C_0 (V_{gs} - V_t) \sim \left(2 \frac{W}{L} \mu_n C_0 I_d\right)^{1/2} \text{ [mhos]}.$$

(5.4)

Equations (5.3) and (5.4) approximate the action of MOSFETs that are in strong inversion ( $V_{gs} > V_t$ ). MOSFETs in weak inversion are discussed later in this chapter for the specific case of a direct injection preamplifier.

#### 5.3 TRANSISTOR NOISE

Although most modern ROICs are comprised of MOSFETs and other components formed in CMOS integrated circuit technology, MOSFETs are not always

the best choice for low noise amplification of detector signals. There is a strong relationship between detector impedance and optimum readout technology. Although the silicon MOSFET covers most infrared applications, it is not well suited for all detectors. Specifically, discrete readout preamplifier implementations, popular in systems with few detector elements, can benefit from BJT, JFET, or MOSFET technology.

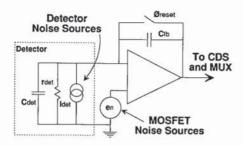

Detectors can be divided into two impedance categories: low-impedance sensors (lower than  $10~k\Omega$ ), such as long-wave IR photoconductive HgCdTe detectors, and high-impedance sensors (greater than  $10~k\Omega$ ), such as photovoltaic, extrinsic silicon, and platinum-silicide detectors. Noise in detectors is generated by the incident photon flux as well as inherent noise sources in the detecting element itself. The input active device of the ROIC preamplifier, a transistor, is usually the dominant noise contributor of the readout. The preamplifier should provide enough gain to balance, if not render negligible, downstream noise source contributions. If this is the case, the input transistor becomes the principal factor in readout noise performance.

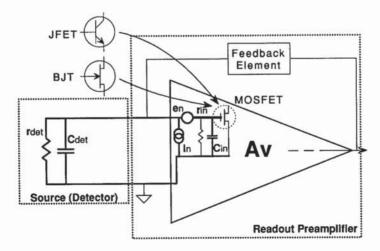

The noise contribution of the input transistor is a function of the source impedance presented by the detector. Thus, it is important to match the detector with an appropriate readout input transistor. A schematic representation of a detector and the input transistor of an amplifier are shown in Fig. 5.5. The functions  $e_n$  and  $i_n$  are the equivalent input noise voltage and current of the transistor and are usually expressed in terms of noise power spectral density versus frequency. It can be generalized that a high transistor noise current, coupled with a high-impedance detector, can result in high-noise gain on the input node. Conversely, a low-impedance detector can tolerate high-noise current but will suffer from high-noise voltages. The equivalent input noise voltage  $e_{\rm in}$  for a transistor or preamplifier in a voltage mode amplifier configuration is given by

Fig. 5.5 Input referred noise of the preamplifier is usually driven by the input transistor. MOSFETs and JFETs have low  $i_n$ , while BJTs have low  $e_n$ .

$$e_{\rm in} \approx \left\{ \left[ \frac{e_n r_{\rm in}}{(r_{\rm in} + r_s)} \right]^2 + (i_n r_{\rm in} || r_s)^2 \right\}^{1/2} \approx [e_n^2 + (i_n r_s)^2]^{1/2} \quad [V/\sqrt{\rm Hz}]$$

(5.5)

for the nominal case where the voltage mode amplifier input impedance  $r_{\rm in}$  is very high. The impedance  $r_{\rm in} \| r_s$  is the parallel combination formed by the input impedance of the amplifier (or transistor) and the source resistance. The output referred noise is the product of  $e_{\rm in}$  and the voltage gain of the amplifier  $A_v$ . In current-to-voltage, or transimpedance, amplifiers, it is useful to express the noise in terms of an equivalent input noise current,  $i_{\rm in}$ , instead of a voltage:

$$i_{\rm in} \approx \left\{ \left[ \frac{i_n r_s}{(r_{\rm in} + r_s)} \right]^2 + \left( \frac{e_n}{r_{\rm in} \| r_s} \right)^2 \right\}^{1/2} \approx \left[ i_n^2 + \left( \frac{e_n}{r_s} \right)^2 \right]^{1/2} \quad [A/\sqrt{\rm Hz}]$$

(5.6)

for the nominal case of a transimpedance amplifier where the input resistance is very low. The output referred amplifier noise is the product of  $i_{\rm in}$  and the amplifier transimpedance  $Z_t$ .

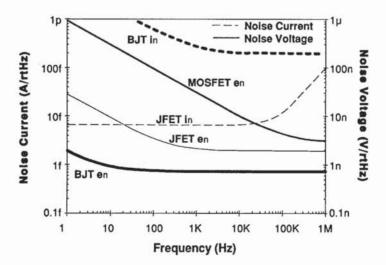

Noise current and voltage for typical low-noise transistor technologies in the common source (or common emitter) configuration are plotted in Fig. 5.6. The noise is typical for low-noise devices such as discrete JFETS and BJTs, as well as for MOSFETs that might be found in a CMOS integrated circuit. Noise data for discrete BJT and JFETS are available from manufacturer's data books, whereas integrated circuit MOSFET noise is typically measured and modeled statistically for a given integrated circuit process and transistor geometry.

Within the system bandwidth of interest, the characteristics of  $e_n$  and  $i_n$  may not be flat with frequency, that is, white noise. These characteristics may

Fig. 5.6 Noise voltage and currents for typical low-noise BJTs, JFETs, and MOSFETS. MOSFET noise current is negligible.

be boosted at low frequencies, as is the case for 1/f noise, or boosted at high frequencies. Therefore, the total output rms noise must be calculated by integrating the power spectral densities, plotted in Fig. 5.6, for example, over the equivalent noise power bandwidth required, and then multiplying this by the gain of the amplifier:

$$v_{\text{out}}^{2}(e_{n}) = \int_{f_{\text{low}}}^{f_{\text{high}}} A_{v}^{2}(f) e_{\text{in}}^{2}(f) df \quad [V^{2}] , \qquad (5.7)$$

or, for a transimpedance amplifier,

$$v_{\text{out}}^{2}(i_{n}) = \int_{f_{\text{low}}}^{f_{\text{high}}} Z_{t}^{2}(f) i_{\text{in}}^{2}(f) df \quad [A^{2}] , \qquad (5.8)$$

where  $A_v$  and  $Z_t$  are the voltage gain and current transimpedance, respectively. The total rms output noise voltage from all noise components is summed in the power domain, for example,

$$v_{\text{out}} (\text{total}) = [v_{\text{out}}(i_p)^2 + v_{\text{out}}(i_{\text{det}})^2 + v_{\text{out}}(i_{\text{ph}})^2 + ...]^{1/2} [\text{volts rms}] .(5.9)$$

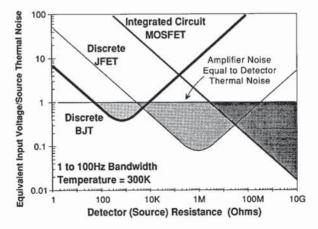

Figure 5.7 shows the ratio of amplifier (or input transistor) noise to detector thermal noise, as a function of detector source resistance, for the BJT, JFET, and MOSFET examples in the common emitter or source configuration. The calculations for detector (and resistor) thermal noise are covered later in this chapter. Notice that for photovoltaic detectors, which typically have impedances above 1 M $\Omega$ , MOSFET noise under the conditions given is lower than the detector thermal noise. MOSFETs, however, are not the optimum choice for detectors with impedance below 100 k $\Omega$ , such as some low-resistance photoconductors; bipolar transistors are the best choice in these cases. JFETS,

Fig. 5.7 Bipolar transistors offer low noise for low-impedance detector applications, while JFETs and MOSFETs offer low noise for high-impedance detectors.

common in discrete amplifier circuit configurations, offer greater performance than MOSFETs out to 100 M $\Omega$ , even at room temperature; and, although not shown, cooled JFETS have continued low-noise performance well beyond 100 M $\Omega$ , because shot-noise-inducing input bias current is significantly reduced with temperature.

There are two primary sources of noise in MOSFETs. The white (flat with frequency) channel thermal noise, usually input referred as a voltage from gate to source, is given as

$$e_n = \left(\frac{\frac{8}{3}k \ T\Delta f}{g_m}\right)^{1/2} \quad [V] \tag{5.10}$$

for both MOSFETs and JFETs. Unpublished data indicate that the actual channel thermal noise on some MOSFETs may be higher than that predicted here.

MOSFET 1/f noise comes primarily from current fluctuations caused by surface states at the interface of the MOSFET channel and the gate oxide. These surface states capture an electron (or hole) and release it at a later time. The 1/f noise is a strong function of the CMOS process and can vary significantly from one process lot to another. In general, 1/f for a given process can be reduced through circuit design by increasing the gate area, WL, or the gate capacitance,  $C_{0x}$ , of the MOSFET

$$e_{n(1/f)} \propto \left(\frac{1}{WLC_0 f^{\alpha}}\right)^{1/2} \left[V/\sqrt{\text{Hz}}\right],$$

(5.11)

where  $\alpha$  is normally modeled as -1.0, but can vary between process lots.

# 5.4 ROIC PERFORMANCE DRIVERS

Sensor electronic designs, whether discrete or ROIC, are guided by requirements traceable to system performance parameters or input/output interface requirements. Key ROIC requirements are matched with respect to key system or interface requirements in Table 5.2.

The SNR is the prime design driver in most sensor systems. To achieve SNR objectives, trade-offs must often be made between detector temperature, circuit area, and power. Other important drivers include dynamic range, linearity, and operability. All requirements are interrelated and can usually be met given great enough real estate (detector size), power, and a low detector temperature. These conveniences are rarely allowed, resulting in designs requiring many trade-offs and compromises between parameters. The designer should develop a dialog with the sensor user so that the evolving design accurately reflects the users needs.

#### 5.5 ROIC PREAMPLIFIER OVERVIEW

Most ROICs utilize preamplifiers that accumulate detector photon-induced current over a fixed integration time. The detector current, accumulated in an

system noise floor

EMI from environment

crosstalk between multiplexed elements

| Major Readout Performance<br>Parameters | Related System Parameter or Interface Impact           | Comments  Minimized to enhance SNR                              |  |  |

|-----------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------|--|--|

| NEC (noise equivalent charge)           | Sensitivity                                            |                                                                 |  |  |

| Power dissipation                       | Cooldown time<br>Life<br>Weight                        | Limited cryogen/cooler life<br>Cryogen weight/cooler size       |  |  |

| Dynamic range                           | Maximum saturation signal                              | Loss of signal                                                  |  |  |

| Crosstalk                               | System MTF (resolution) Blooming of saturated elements | Element to element                                              |  |  |

| Frequency response                      | System MTF (resolution)<br>Latent images               | Often related to crosstalk                                      |  |  |

| Input impedance                         | Signal linearity<br>Noise                              | Detector bias changes with signal Loss of optimum detector bias |  |  |

| Linearity reliability                   | Calibration<br>Instrument life                         | Proper identification<br>Confidence of success                  |  |  |

| Gain                                    | Sensitivity                                            | Signal amplified above                                          |  |  |

Sensitivity

MTF

Output video driver

impedance

Table 5.2 Relationships between Key Readout Circuit Requirements and System Performance and Interface Issues

integration capacitor or CCD "bucket," results in a signal that is periodically sampled and multiplexed out of the preamplifier. The integration capacitor is reset and the process starts over again. A less common form of ROIC preamplifier provides continuous output voltage or current, which is proportional to the detector current, in lieu of an accumulated signal at the end of the frame time. The most common families of preamplifiers and their typical performance capabilities are given in Table 5.3. It is worth noting that the listed performance capabilities represent typical preamplifier applications and that it is possible, through careful design, to broaden the application space of the various configurations. Each of these configurations is briefly described here and then treated in detail in later sections. Many of these circuits and related topics are also addressed by Nelson, Johnson, and Lomheim.9

The self-integrator (SI) has the fewest unit cell components among all readout circuit configurations. Photon-induced charge is integrated over a given frame time directly onto the integration capacitance formed on the detector node, and is periodically transferred out of the unit cell via the multiplexer switch (MUX). The output of the SI is in the charge domain as opposed to the voltage domain. The action of the MUX, while enabled, resets the integration capacitor at the end of each frame.

A buffer amplifier can be added to the SI to provide voltage domain readout to the MUX. This implementation, normally a MOSFET source follower per detector (SFD), requires a reset switch on the detector node to reset the integration capacitor, because the MUX cannot provide reset through the buffer.

| Circuit                                  | Block Diagram   | Circuit<br>Descrip-<br>tion               | Minimum<br>Multiplexer<br>Required<br>(MUX)     | Typical<br>Noise (e')<br>at Frame<br>Rate** | Dynamic<br>Range<br>V <sub>sat</sub> v <sub>ns</sub> | Frequency<br>Response<br>(KHz) | Power<br>Per Cell<br>(µW) | Non-<br>Linearity               | Detector<br>Bias<br>Uniformity | Minimum<br>Unit Cell<br>Area<br>(µmxqam) | Irradiance<br>Range at<br>1KHz F.R.<br>(ph/cm <sup>2</sup> /s) |

|------------------------------------------|-----------------|-------------------------------------------|-------------------------------------------------|---------------------------------------------|------------------------------------------------------|--------------------------------|---------------------------|---------------------------------|--------------------------------|------------------------------------------|----------------------------------------------------------------|

| SI -<br>Self<br>Integrator               | ph MUX Det Tont | Reset<br>Integrator                       | CCD or<br>Active Amp.<br>Prior to<br>Video Amp. | 400 at<br>1KHz                              | ≥200<br>High Noise<br>Low Signal                     | >200                           | <0.5µW                    | Tracks<br>Detector<br>I-V       | ~1mV to<br>10mV                | <10 x <10                                | <1x10 <sup>9</sup> to<br>-3x10 <sup>14</sup>                   |

| SFD -<br>Source<br>Follower/<br>Detector | ~ [F] ~         | Buffered<br>Reset<br>Integrator           | Video<br>Amplifier                              | 50 - 100<br>at 10Hz                         | ~2,000<br>Low Signal                                 | >200                           | ~0.5μW                    | Tracks<br>Detector<br>I-V       | 1mV                            | <20 x <20                                | <1x10 <sup>9</sup> to<br>-3x10 <sup>14</sup>                   |

| CTIA -<br>Capacitor<br>Feedback<br>TIA   | 4000            | Miller<br>Reset<br>Integrator             | Video<br>Amplifier                              | 40 - 150<br>at 10KHz                        | >10,000 -<br>Low Noise<br>High Signal                | >200                           | 3μW -<br>40μW             | Reduced<br>By Amp.<br>Feedback  | <0.5mV*<br>(to 40mV)           | 35 x 35                                  | <1x10 <sup>9</sup> to<br>-3x10 <sup>15</sup>                   |

| DI -<br>Direct<br>Injection              | 74 (T)          | Injection<br>Reset<br>Integrator          | Same as<br>FEDI                                 | 80 at<br>10KHz                              | ~2,500<br>Medium<br>Noise                            | >20<br>at Higher<br>Flux       | <0.5µW                    | Tracks<br>MOSFET<br>& Det. I-V  | 10mV to<br>40mV                | <20 x <20                                | 1x10 <sup>12</sup> to<br>-4x10 <sup>15</sup>                   |

| FEDI -<br>Feedback<br>Enhanced<br>DI     | 7 T             | Injection<br>Reset<br>Integrator          | CCD or<br>Active Amp.<br>Prior to<br>Video Amp. | 80 at<br>10KHz                              | 5,000                                                | >50                            | 6μW -<br>30μW             | Reduced By<br>Open Loop<br>Gain | <0.5mV*<br>(to 40mV)           | 40 x 40                                  | 1x10 <sup>11</sup> to<br>~3x10 <sup>15</sup>                   |

| CM -<br>Current<br>Mirror                |                 | Gate<br>Modulation<br>Reset<br>Integrator | CCD or<br>Active Amp.<br>Prior to<br>Video Amp. | 1,000<br>at 10KHz                           | ~2,000<br>High Noise<br>High Signal                  | >20                            | <0.5µW                    | Tracks<br>MOSFET<br>I-V         | 10 to<br>40mV                  | 30 x 30                                  | 1x10 <sup>13</sup> to<br>>5x10 <sup>16</sup>                   |

| RL -<br>Resistor<br>Load                 |                 | Gate<br>Modulation<br>Reset<br>Integrator | CCD or<br>Active Amp.<br>Prior to<br>Video Amp. | 10,000<br>at 10KHz                          | ~2,000<br>High Noise<br>High Signal                  | >20                            | <0.5µW                    | Tracks<br>Resistor<br>I-V       | 10 to<br>40mV                  | 30 x 30                                  | 1x10 <sup>13</sup> to<br>>5x10 <sup>16</sup>                   |

| RTIA -<br>Resistor<br>Feedback<br>TIA    | 2000            | Current<br>to Voltage<br>Amplifier        | Video<br>Amplifier                              | 60 - 150 at<br>1KHz                         | >10,000<br>Low Noise<br>High Signal                  | >50                            | 12μW -<br>500μW           | Reduced<br>By Amp.<br>Feedback  | <0.5mV*<br>(to 40mV)           | 100 x 100                                | <1x10 <sup>9</sup> to<br>>5x10 <sup>16</sup>                   |

Table 5.3 Common ROIC Preamplifiers Selected According to the Limitations and Performance Requirements of the Specific Application

The detector bias of both the SI and SFD, although initially set at the beginning of a frame, changes as detector current integrates onto the input node. This detector debias results in signal output nonlinearity, since the signal characteristics of many detectors change as a function of bias. Neither the SI nor the SFD provides gain within the unit cell.

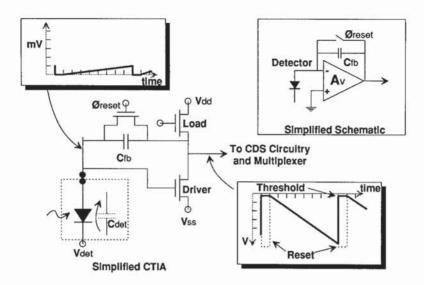

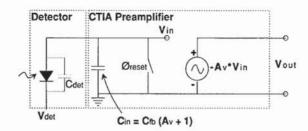

The capacitor feedback transimpedance amplifier (CTIA) solves the debias and gain limitations of the SFD and SI by incorporating the integration capacitor into the feedback loop of an inverting, high-gain differential amplifier, and thereby forcing charge to integrate into the feedback capacitor instead of the detector node capacitance. This results in a stable detector bias with a more linear signal transfer function. Because its gain is set by the feedback capacitor instead of the detector node stray capacitance, the CTIA can provide a high degree of signal amplification prior to multiplexing. The trade-off is that the CTIA requires significantly more area to implement than either the SI or the SFD.

Direct injection (DI) circuits provide a low-impedance detector interface, via the source of a MOSFET, that helps to keep the detector bias constant. Photon-induced charge integrates onto the capacitor at the drain of the MOSFET. The gain of the DI is set by the integration capacitor and, like the CTIA, gain can be quite high. The DI is limited to medium to high photon flux ranges. This is because the input impedance increases dramatically at low detector current levels, resulting in unstable detector bias, lower photon current integration, and reduced frequency response on the detector node. Also, since the input node of the DI is not reset at the end of each integration period, charge induced

<sup>\*</sup> Lower Detector Bias Offset Achievable Utilizing Auto-Zeroing Type Amplifier

\*\* Detector Capacitance in 0.3pf to 1pF Range

in one frame of data can be integrated during the subsequent frame, resulting in reduced frequency response.

Feedback-enhanced DI (FEDI) incorporates an inverting amplifier between the detector node and the input MOSFET gate. This further reduces input impedance for applications at lower backgrounds. Like the SI, both the DI and FEDI provide charge domain output to the MUX; voltage mode output can be accomplished by adding a SFD to the output of the DI or FEDI.

Due to real estate constraints, it is not possible to accumulate all of the photon-induced charge at very high irradiance levels on a capacitor within the unit cell. Hence, the photon current must be scaled down before integration onto a reasonable size integration capacitor. For such applications, the current mirror (CM) preamplifier utilizes a load MOSFET, biased by the detector photon current, to induce or mirror a smaller current in the drain of a scaled down input MOSFET. The resistor load (RL) circuit provides a similar function by utilizing a resistor load in the detector to induce a lower current in the input MOSFET for accumulation onto the integration capacitor. Both CM and RL circuits suffer the same frequency response and detector bias stability issues as DI circuits.

The RTIA is similar to the CTIA but with the feedback capacitor and reset switch replaced by a resistor. The RTIA does not integrate detector current; rather, it provides a continuous output voltage that is proportional to the detector current. Since it is not reset after data are sampled, the RTIA has limitations in frequency response. It also requires high resistance feedback to provide gain comparable to the CTIA; large resistors require considerable unit cell area while tending to be high in 1/f noise or drift.

# ROIC Preamplifier Signal-to-Noise Ratio

Sensitivity is normally the most important and challenging user-imposed requirement of a sensor design. Sensitivity can be expressed in terms of SNR or some other related parameter. The benchmark SCA performance parameters for SNR are typically functions of the sensor application, as given in Table 5.4. A common detector sensitivity parameter  $D^*$  is not a reasonable sensor flowdown, because high  $D^*$  can be achieved without fully addressing the system

| Parameter | Definition                                                                                     | Units                              | Common Application                                                                       |  |  |

|-----------|------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------------------------------------------------------------|--|--|

| NEdT      | Noise equivalent temperature                                                                   | K                                  | Thermal imagers                                                                          |  |  |

| NEI       | Noise equivalent irradiance                                                                    | ph/cm <sup>2</sup> s <sup>-1</sup> | Radiometers and photon counters                                                          |  |  |

| NEP       | Noise equivalent power                                                                         | W                                  | Imagers and radiometers                                                                  |  |  |

| NEC       | Noise equivalent charge (in a data frame)                                                      | e <sup>-</sup>                     | Measure of ROIC,<br>preamplifier, and CCD<br>sensitivity<br>Astronomy<br>Visible imagers |  |  |

| $D^*$     | Signal-to-noise normalized to<br>photon energy, optical area,<br>and system power<br>bandwidth | A √Hz/W<br>(Jones)                 | Comparison of detector technologies                                                      |  |  |

Table 5.4 Heaful Sensitivity Parameters Polated to Sensor Amplications

SNR requirements. However,  $D^*$  is a valued tool for comparing one detector technology to another, since it is normalized to signal power, signal power bandwidth, and detector optical area.

Readout and SCA sensitivity are most often expressed in terms of any number of input referred noise quantities. Noise equivalent sensitivity parameters can be interpreted as the signal level that would result in a SNR of unity. The most universal measurement of readout sensitivity is noise equivalent charge (NEC); that is, the equivalent input referred noise electrons accumulated over a single frame or sample of data. NEC is specified with a given signal bandwidth or frame rate of interest. For a readout circuit that accumulates photon charge on an integration capacitor, NEC is the equivalent noise charge on the integration capacitor. The most commonly specified SCA level sensitivity parameter is noise equivalent irradiance (NEI), or the equivalent input irradiance for a SNR of unity; NEI holds the designer to a specific SNR at the sensor output. NEC can be referred to the input of the sensor, in terms of NEI through

$$NEI = \frac{NEC}{\eta A_{\text{opt}} t_{\text{int}}} \left[ ph/cm^2 s^{-1} \right] , \qquad (5.12)$$

where  $\eta$  is the quantum efficiency of the detector,  $A_{\rm opt}$  is the detector optical area, and  $t_{\rm int}$  is the integration time over which photon charge accumulates.

# 5.5.2 System Sensitivity Flowdown

In general, the readout circuit is an integral part of the sensor design and should not be separated from the SCA or higher level assemblies. Therefore, sensor requirements must be partitioned into detector, readout, and other subcomponent parameters before design work can begin. Although subcomponents such as off-focal-plane amplifiers and digitizers require an allocation of the specification space, these parts are well understood and will be assumed to have negligible system impact in the following analyses.

An example flowdown of sensor sensitivity to the detector and readout begins by dividing the SCA level NEI into two equal noise contributors. This initial allocation is made after contributions from the photon flux  $Q_B$  are removed from the system NEI:

$$NEI_{SCA} = (NEI_{sys}^2 - NEI_{ph}^2)^{\frac{1}{2}} = \left(NEI_{sys}^2 - \frac{Q_B}{\eta A_{opt}t_{int}}\right)^{\frac{1}{2}} [photons] \quad (5.13)$$

for photovoltaic detectors. In this case, the sum of the readout contribution,  $NEI_{ro}$ , and the detector contribution,  $NEI_{det}$ , yields the SCA total ( $NEI_{SCA}$ ). The initial detector and readout allocations are

$$NEI_{ro} = NEI_{det} = \frac{NEI_{SCA}}{\sqrt{2}}$$

[photons], (5.14)

which is an approximation, since it does not allocate NEI to other second-order noise contributors such as the multiplexer, video driver, off-focal-plane electronics, and the digitizer.

**Detector NEI.** The value of NEI<sub>det</sub> is determined, to first order, from the noise contribution of a photovoltaic detector in reverse bias<sup>6</sup>:

$$i_{\text{det}} = (2qI_{\text{dark}}\Delta f)^{1/2} \quad [\text{amps rms}] ,$$

(5.15)

where the detector noise current is assumed to be white thermal noise, q is the electron charge,  $\Delta f$  is the measurement bandwidth, and  $I_{\rm dark}$  is the backbias dark current of the detector. The total (rms) detector noise is determined by integrating the noise and noise transfer function over all frequencies. For a photon integrating sensor, in which detector charge is accumulated and periodically read out before reset, the transfer function of the accumulator drops the noise power bandwidth and noise rolls off at a frequency of approximately

$$f \approx \frac{1}{2T_{\text{frame}}}$$

[Hz], (5.16)

where  $T_{\rm frame}$ , the period between frames, is approximately equal to the integration time. (The shape of various transfer functions in a sampled system will be covered in a subsequent section.) Since the shot noise in Eq. (5.15) is white, i.e., flat over all frequencies, the noise power bandwidth of the accumulator can be substituted for  $\Delta f$ . The total number of noise electrons, or NEC, accumulated in a given integration time is

$$NEC_{det} = \frac{i_{det}t_{int}}{q}$$

[electrons] . (5.17)

To fit within the allocated NEI,

$$NEI_{det} > \frac{NEC_{det}}{\eta A_{opt} t_{int}} = \left(\frac{I_{dark}/t_{int} q \eta^2}{A_{opt}}\right)^{1/2} [ph/cm^2 s^{-1}],$$

(5.18)

resulting in a maximum dark current of

$$I_{\text{dark}} < \text{NEI}_{\text{det}}^2 \eta^2 q A_{\text{opt}} \quad [\text{amps rms}] .$$

(5.19)

As a note, the NEI contribution from the photon-induced noise is calculated by replacing the dark current  $I_{\text{dark}}$  with photon current  $I_{ph}$  in the preceding equations.

For detector operation near zero bias, where dark current is negligible, the detector thermal noise can be expressed in terms of the small-signal detector resistance at zero bias,  $R_0$ , and the temperature of operation,  $T_{\text{det}}$ :

$$i_{\text{det}} = \left(\frac{4kT_{\text{det}}\Delta f}{R_0}\right)^{1/2} \quad [A] , \qquad (5.20)$$

where k is the Boltzmann constant. This yields a maximum detector noise contribution of

$$NEI_{det} > \frac{(2kT/t_{int}R_0)^{1/2}}{q\eta A_{opt}} [ph/cm^2 s^{-1}], \qquad (5.21)$$

and a minimum zero-bias resistance,

$$R_0 > \frac{2kT}{t_{\text{int}} NEI_{\text{det}}^2 q^2 \eta^2 A_{\text{opt}}^2} \quad [\Omega] . \tag{5.22}$$

Both of these expressions for detector thermal noise, Eqs. (5.19) and (5.22), are approximations that fit well in specific regions of detector operation. Equation (5.21) is most commonly used in infrared photovoltaics, because detector bias is usually minimized to reduce dark current and, therefore, detector 1/f noise (drift). Detector performance is often expressed in terms of  $R_0A_{\rm opt}$ , or  $I_{\rm dark}$ , and  $\eta$  due to their dependence on noise as expressed in Eqs. (5.18) and (5.21). If the selected detector technology shows significant margin in these parameters, more of the total noise budget can be allocated to the readout or other downstream noise sources.

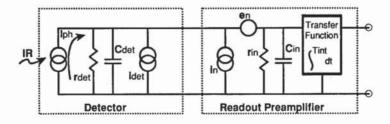

**Readout NEI.** Readout noise, which is a function of the circuit configuration and layout details, is more difficult to analyze than detector noise. All readout circuits can be conceptualized in a format similar to that shown in Fig. 5.8, in which the readout noise sources are combined into an equivalent input referred noise voltage  $e_n$  and noise current  $i_n$ . Both parameters are usually dominated by the noise of the preamplifier input transistors and their sampled transfer function to the output. In determining the values of  $e_n$  and  $i_n$ , the folding, or aliasing, of high-frequency noise into the system bandwidth of interest must be considered.

Once the appropriate input noise contributions are determined, the readout amplifier noise current is handled in the same way as detector noise current in Eq. (5.17); however, the input referred noise voltage must be converted to an equivalent current prior to applying it to Eq. (5.17):

$$i_{en} = \frac{e_n}{r_{\text{det}} || r_{\text{in}}} \quad [\text{amps rms}] , \qquad (5.23)$$

Fig. 5.8 Simple model of the sensor includes detector noise current and amplifier input referred noise voltage and current. Most preamplifiers can be conceptualized in this manner.

where  $r_{\text{det}}||r_{\text{in}}$  is the parallel combination of the small-signal detector and the amplifier input resistances. The NEC of the readout, with a fixed integration time of  $t_{\text{int}}$ , is

$$NEC = \left[ i_n^2 + \left( \frac{e_n}{r_{\text{det}} || r_{\text{in}}} \right)^2 \right]^{1/2} t_{\text{int}} \quad \text{[electrons]}$$

(5.24)

and is input referred to the detector as

$$NEI_{ro} > \frac{NEC}{\eta A_{opt}t_{int}}$$

[photons] . (5.25)

Equations (5.24) and (5.25) can be utilized to determine the maximum noise contribution of the readout through Eq. (5.13). The results will guide the readout circuit type and design. Allocation of sensitivity should be made to detector drift, as well as to other less critical components not covered here, such as off-focal-plane electronics.

#### 5.6 READOUT PREAMPLIFIERS

This section covers many of the most common readout preamplifier circuit families. Although the focus is on integrated circuit forms of the preamplifier, the RTIA is covered because it is utilized in sensors with few detector elements, it can be fabricated in ROIC format, and it provides an introduction to noise concepts necessary for subsequent preamplifier circuits.

# 5.6.1 Analysis of the Resistor Transimpedance Amplifier

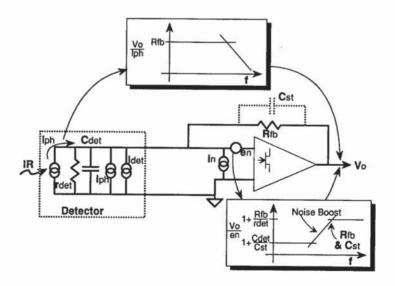

The analysis tools discussed can be demonstrated and expanded by example for a common detector preamplifier circuit, the resistor transimpedance amplifier. The RTIA, usually employed in discrete rather than integrated circuit configurations, is useful in systems requiring only a few pixels (detector elements). The RTIA is also readily adaptable to ROIC format and may be combined with a sample/hold stage and multiplexers for application in sensors with larger numbers of elements. As with most photovoltaic readout amplifiers, the RTIA is a transimpedance or current-to-voltage amplifier. Unlike most preamplifiers, it does not accumulate, or integrate, signal charge over a given frame time; instead it presents a continuous output signal proportional to the input (photo) current. A schematic of a generic RTIA in a focal plane application, along with the predominant noise sources, is presented in Fig. 5.9.

The output response of the RTIA to a photon-generated current, or to any input current including noise, is

$$Z_t(f) = \frac{V_{\text{out}}}{I_{ph}} = \frac{R_{fb}}{\left[1 + (2\pi f R_{fb} C_{st})^2\right]^{1/2}} \quad [V/A] . \tag{5.26}$$

The in-band low-frequency transimpedance  $Z_t$  is set by  $R_{fb}$ , which is selected to provide sufficient gain to the system and to minimize its thermal noise contribution.

Noise contributed by the feedback resistor can be represented as a noise current across either the resistor or the input node by<sup>6</sup>:

$$i_{Rfb} \approx \left(\frac{4kT\Delta f}{R_{fb}}\right)^{1/2} \quad [A] \quad .$$

(5.27)

It is normally desirable to keep the feedback resistor noise below the detector thermal noise of Eq. (5.20); this results in a preliminary selection of  $R_{fb}$  as

$$R_{fb} > R_0 \frac{T_{Rfb}}{T_{\text{det}}} \quad [\Omega] . \tag{5.28}$$

If the feedback resistor is on the focal plane and its temperature,  $T_{Rf}$ , is the same as that of the detector,  $T_{\text{det}}$ , then  $R_{fb}$  must be greater than the zero-bias resistance of the detector,  $R_0$ . If  $R_{fb}$  is too large, the very high amplifier transimpedance will result in saturation of the output signal.

If photon-induced noise is greater than detector thermal noise, then the feedback resistor is optimized to have lower noise than the photon-induced noise current  $i_{ph}$ :

$$i_{ph} = (2qI_{ph}\Delta f)^{1/2} \quad [A] ,$$

(5.29)

then

$$R_{fb} > \frac{2kT_{Rfb}}{I_{ph}} \quad [\Omega] \quad . \tag{5.30}$$

Fig. 5.9 The limits of the RTIA amplifier function are dominated by stray capacitance elements across the feedback resistor and on the input node.

Equations (5.29) and (5.30) can be used as guidelines for determining a reasonable transimpedance for the preamplifier. It may be desirable to have a higher  $R_{fb}$  than expressed above in order to further reduce its noise contribution and thus further limit its impact on the total noise, or to provide higher gain upfront and thus reduce the impact of downstream noise sources.

The feedback resistor must be selected with careful consideration to drift, or 1/f noise, which is common in high-ohmage resistors. In general, large surface area resistors exhibit low 1/f but, because of size, these are not easily integrated into cold focal plane configurations. Before committing to a final design, sample resistors should be measured both for 1/f and temperature stability, because any change in transimpedance with temperature can manifest as noise.

After selecting an appropriate transimpedance for the amplifier, the design should focus on selection of a low-noise-differential amplifier for RTIA implementation. Shot noise current of the amplifier, which is dependent on the input bias current of the input transistor,  $I_{\rm in}$ , is governed by the same equation that predicts noise from photon current, and can be estimated at the input node as

$$i_n = (2qI_{in}\Delta f)^{1/2}$$

[A] . (5.31)

Input bias current should be much less than the photon current, and in such cases shot noise is insignificant. For JFETs, this approximation can lose accuracy at very low frequencies where transistor 1/f, or drift components, can dominate. Also, since input bias current is a strong function of temperature for JFETs,  $i_{\rm in}$  can be negligible at cryogenic temperatures. Shot noise in MOSFETs is insignificant compared to the thermal noise of most detectors, provided no leaking p-n junctions or other stray current paths exist on the input node.

Transistor input referred noise voltage,  $e_n$ , does not have the same transfer function to the output as photon signal current in the RTIA. In the case of MOSFETs and JFETs, this noise is predominantly the channel thermal and 1/f noise described earlier in Eq. (5.10). The most straightforward way to analyze the impact of the input referred noise voltage is to refer to it as a noise current, by first determining its characteristics at the output node (through the amplifier) and then dividing by the circuit transimpedance. This allows all noise sources on the input node to be directly compared and summed as a single noise current. In Fig. 5.9, the transfer function of  $e_n$  to the output node is flat at low frequencies. At higher frequencies the stray capacitance on the input node "boosts" the voltage gain of the transfer function and noise gain increases. Eventually, the response goes flat again as parasitic or other capacitors across the feedback resistor become the dominant transimpedance element:

$$\frac{v_{\text{out}}}{e_n} = \left\{ 1 + \frac{R_{fb}}{R_{\text{det}}} \left[ \frac{1 + (2\pi f C_{\text{det}} R_{\text{det}})^2}{1 + (2\pi f R_{fb} C_{fb})^2} \right] \right\}^{\frac{1}{2}} \quad [V/V] . \tag{5.32}$$

The input referred equivalent noise current caused by  $e_n$  of the RTIA is the ratio of Eq. (5.32) to Eq. (5.26):

$$i_{en}(f) = e_n \left( \frac{1}{R_{fb}} + \frac{1}{R_{det}} \right) \left[ 1 + (pfC_{det}R_{det})^2 \right]^{1/2} [A/\sqrt{Hz}]$$

(5.33)

The total input referred noise current of the dominant RTIA noise sources is the sum of the photon, detector, feedback resistor, and transistor noises in the power domain:

$$i_{\text{total}} = (i_{ph}^2 + i_{\text{det}}^2 + i_n^2 + i_{en}^2)^{1/2} [A/\sqrt{Hz}].$$

(5.34)

The total noise should be compared to the system noise allocation discussed previously.

A detector and amplifier combination, such as the RTIA with a photovoltaic detector, are said to be "BLIP" (background limited performance) if the total noise is equal to the photon noise. The percent BLIP is calculated by dividing the photon noise by the total sensor noise, in this case Eq. (5.34),

$$\% BLIP = \frac{i_{ph}}{I_{\text{total}}} \times 100 . \qquad (5.35)$$

The same BLIP can also be calculated via other sensitivity parameters such as  $D^*$ , SNR, and NEI.

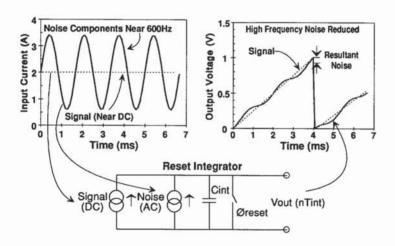

# 5.6.2 Reset Integrators and Sampled Readout Circuits

The RTIA is commonly applied in a discrete component configuration in systems with few detector elements. However, the nature of most SCA applications is such that hundreds to thousands of detector elements must be amplified and multiplexed onto a few output lines in an integrated circuit configuration. In many cases, simple integrated circuit capacitors and switches act as the gain setting element in place of the resistor utilized in the RTIA. To design for and analyze the sensor sensitivity requires additional steps beyond those discussed in the previous section. A common problem encountered in switched circuit analysis is the aliasing of high-frequency signals or noise into the bandpass of the sampled signal, thereby producing a false signal or increasing noise beyond normal expectations.

An example of this aliasing effect can be seen in the spoked cartwheels of Western movies. The wheels appear to be moving slowly, stopped, or even reversed although the wagon is obviously moving forward at a high rate of speed. The cartwheel spokes are sampled by the film at a rate of 30 Hz. If the wheel passes a reference point in the camera's field of view at a rate of 29 spokes per second, the wheel will appear to be moving in reverse at about 1 spoke per second; this is because each subsequent spoke is imaged in a position slightly behind that of the preceding spoke in the previous frame. If the spokes are moving at exactly 30 or 60 per second, the camera will image subsequent spokes in the same position on each frame of film, giving the appearance of no spoke, or wheel, movement at all. These same effects are seen in sampled sensor systems, where undesirable high-frequency noise, signal, or interference appears at frequencies below half the scene sample rate, the so-called Nyquist rate or limit.

Sensors can be divided into two general classes of input preamplifier types: (1) those, such as the previously described RTIAs, that amplify or create a continuous output voltage representing the photon generated signal, and (2) those

that additionally accumulate and average (or integrate) the photon signal over a specified frame time. This second type of sensor is commonly referred to as a reset integrator. The resulting signal from either type of circuit can be multiplexed with other elements. In the analysis that follows, the reset integrators are assumed to integrate during the entire frame time except for a very short reset period.

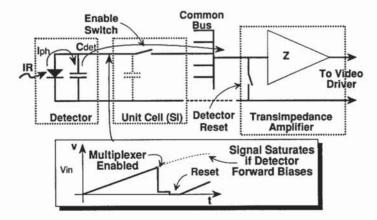

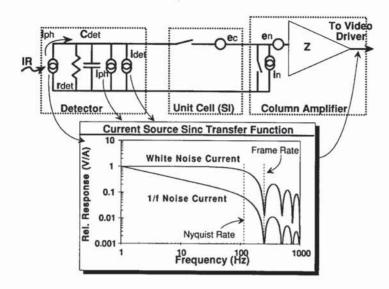

#### 5.6.3 Self-Integrating Readout

Integrating preamplifiers are most commonly used in ROIC designs where the charge accumulation element is a capacitor or a CCD. The capacitor accumulates photon-induced current over an integration period, resulting in a signal that can be multiplexed to the sensor output. Figure 5.10 shows one of the most basic integrating preamplifier unit cell designs, the self-integrator. The SI has advantages over all other designs in that it is composed of a single unit cell readout component, a small MOSFET switch, and thus requires minimum unit cell area. The drawback is that the SI does not provide signal gain in the unit cell and is thus subject to multiplexer and column amplifier noise.

Photon charge in the SI integrates onto the stray capacitance in the unit cell, which is formed primarily by the detector but also includes strays from the interconnect and the MOSFET switch. If necessary, additional capacitance can be added to the readout to increase storage capacity. After charge is integrated for an entire frame, the multiplexer is cycled and the stored charge is transferred onto the low-input impedance transimpedance column amplifier of gain Z. A reset switch on the multiplexer bus normally restores the detector to its pre-integration voltage bias after the amplifier drives the signal out of the multiplexer. However, the action of the transimpedance amplifier may be sufficient to perform the detector reset without the addition of a separate reset switch on the bus. The transfer function of the circuit from photon current to output of the column transimpedance amplifier, over the integration period tint, is

Fig. 5.10 The self-integrator accumulates photon charge on stray capacitance on the input node but provides no gain in the unit cell.

$$V_{\text{out}} = Z \int_{0}^{t_{\text{int}}} I_{ph}(t) dt + ZQ_{r} \quad [V] , \qquad (5.36)$$

where  $Q_r$  is the initial charge stored on the input node and Z is the charge-to-voltage gain.

As the SI integrates photon and dark current onto the detector node capacitance, the voltage bias of the detector forms a ramp, as illustrated in Fig. 5.10. If allowed to integrate too long, however, the detector will become forward biased, resulting in response nonlinearity and additional detector shot noise, as photon-induced charge is shunted across the detector. The ramp on the detector node will follow the current to voltage (I-V) characteristics of the detector. For a photovoltaic detector, the voltage on the input node will follow the characteristics of a diode, which exhibits high nonlinearity as its voltage transitions from reverse to forward bias. The dynamic range of the SI is thus limited to the flat back bias signal excursion of the detector.

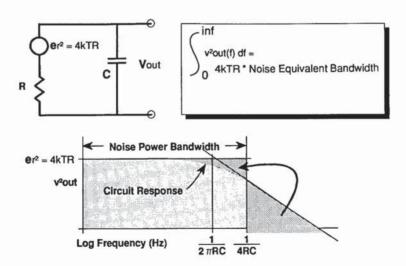

**kTC** Noise. Thermal noise (commonly referred to as kTC noise) is stored on the detector node capacitance at the moment the switch or multiplexer of the SI is disabled (opened). This results in small variations in detector voltage or input node charge  $(\Delta Q_r)$  from one reset time to the next, which in turn results in variation or noise at the end of integration according to Eq. (5.36). This variation in reset voltage is true for any switched capacitor. The thermal noise characteristics of the circuit, when the switch is closed, are the same as in any resistor-capacitor circuit with a resistance  $R_{\rm on}$ :

$$e_R = (4kTR_{\rm on}\Delta f)^{1/2} \quad [V] . \tag{5.37}$$

The rms noise on the capacitor can be calculated by integrating the thermal noise of the resistor over all frequencies through the transfer function of the RC circuit:

$$v_c^2 = 4kTR_{\rm on} \int_0^\alpha \frac{1}{1 + (2\pi f CR_{\rm on})^2} df \quad [V^2] , \qquad (5.38)$$

which can be rewritten as

$$v_c = \left[ 4kTR_{\rm on} \frac{\pi}{2} f(-3 \text{ dB}) \right]^{1/2} = \left( \frac{KT}{C} \right)^{1/2} \text{ [volts rms]} .$$

(5.39)

Notice that the noise produced by resetting a capacitor through a switch is not dependent on the resistance of the switch. In Eq. (5.39), the noise equivalent bandwidth  $[\Delta f]$ , of Eq. (5.37)] is the product of  $\pi/2$  and the -3-dB bandwidth of the circuit, which is true for all white noise sources acted on by a single pole filter. The noise voltage in Eq. (5.39) can also be expressed in terms of noise charge stored on the capacitor by multiplying by the node capacitance:

$$q_c = (kTC)^{1/2} \quad [C] \quad . \tag{5.40}$$

Since kTC noise charge goes up with increased capacitance, it is normal practice to minimize these strays on the input node of the SI. In the case where photon noise dominates, Eqs. (5.29) and (5.40) can be combined to determine the maximum permissible stray capacitance on the input node

$$C ext{ (max)} \ll \frac{i_{ph}t_{ ext{int}}^2}{kT} ext{ [F]} ext{.} ext{(5.41)}$$

Unless special care is taken in the selection of capacitor size, kTC noise can be a dominant noise source in sampled integrated circuit applications. Minimizing this capacitance places special requirements on the detector capacitance; since the detector is normally the dominant contributor to input node capacitance, kTC noise must be considered in all switched capacitor circuits.

Integrated Noise Transfer Function. Individual contributions of all noise sources can be determined by applying the appropriate switched noise transfer function to each source. Noise current on the input node of any integrating amplifier, including the SI, is the simplest to analyze because it has the same transfer function as the signal current  $I_{ph}$ . For this example, the integrated current of the SI forms a voltage on the input node and is reset (transferred) at the end of the integration time, thus possessing the characteristics of the reset integrator. The change in voltage at the end of integration represents, for the SI, the total charge shifted out at the end of integration.

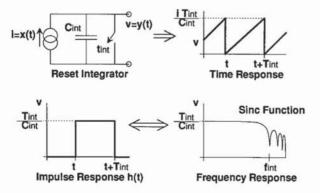

A reset integrator can be modeled as illustrated in Fig. 5.11. The voltage on the input node, shown as a continuous ramp, is the integral of the detector current x(t). The resulting output voltage y(t) can be expressed in terms of the convolution of the input current and the impulse response h(t):

$$y(t) = x(t)*h(t) [V]$$

(5.42)

The impulse response of the reset integrator h(t) over the integration period  $t_{int}$  is

Fig. 5.11 The reset integrator action can be modeled as a continuous integrator that is sampled and subtracted as discrete time increments.

$$h(t) = 1/C_{\rm int} \int_{t-}^{t-+t_{\rm int}} \delta(x) \ dx \quad [V] , \qquad (5.43)$$

which is simply a step to an amplitude of  $1/C_{\rm int}$  at time equal zero, and returns to zero (is reset) after  $t_{\rm int}$ . The integral of the delta function is often referred to as a *window function*, because it applies only to a single integration time, and is zero before integration starts (t-) and after the end of integration.

The frequency response of the reset integrator can be determined by evaluating the Laplace transform:

$$Y(f) = X(f)H(f) \quad [V] , \qquad (5.44)$$

where the Laplace transform of h(t) of Eq. (5.43) is

$$H(f) = \frac{t_{\rm int}}{C_{\rm int}} \frac{\sin(\omega t_{\rm int}/2)}{\omega t_{\rm int}/2} \quad [V/A] , \qquad (5.45)$$

where

$$\omega = 2\pi f \quad [rad/s] \tag{5.46}$$

$$H(f) = \frac{t_{\rm int}}{C_{\rm int}} \frac{\sin(\pi f t_{\rm int})}{\pi f t_{\rm int}} = \frac{t_{\rm int}}{C_{\rm int}} \frac{\sin(x)}{x} \quad [V/A] . \tag{5.47}$$

The sine expression of the form  $\sin(x)/x$  in Eq. (5.47) is commonly referred to as the *sinc function*. This derivation of Eq. (5.47) is strictly valid for an ideal reset integrator that is reset instantaneously in time. In practice, however, some dead time exists between the reset and the onset of integration (due to switching time). Equation (5.47) provides a good approximation in cases where the dead time is a small fraction of the integration time.

Signals that are integrated over time and then reset have the sinc transfer function shown in Fig. 5.12, and are in fact attenuated at frequencies higher than the Nyquist limit. Figure 5.13 shows the result of integrating a slowly changing (dc) photon signal with a high-frequency sine wave riding on it; the high-frequency ac component could be either signal, noise, or interference picked up on the input node. A large net accumulation of signal charge results in this case, through the integration of the dc signal over the entire integration time. The ac noise is also accumulated but tends to cancel out its own excursions above and below the dc signal, thus resulting in a significant reduction in amplitude. Since the integration time is assumed to be nearly equal to the time between frames, the only unaliased frequencies that can pass through the reset integrator are those less than half the frame rate. All other residual energy above the Nyquist frequency is attenuated and "folded" down between Nyquist and zero, thus resulting in higher noise than would otherwise be expected in the passband.

In addition to kTC noise, other noise sources of the SI include detector thermal noise and photon noise, as discussed previously. Also, the column amplifier is usually the major active noise source in most SI designs, although

Fig. 5.12 Simple integrator of the SI provides basis of a sample noise model. Integrated current signal and noise sources have a sinc transfer function.

Fig. 5.13 Noise above the Nyquist frequency is attenuated in integrating amplifiers, reducing any aliasing effects in the passband.

it is outside the unit cell. The noise contribution of the column amplifier is dependent on its type, which can be any one of several unit cell amplifiers discussed later in this section.

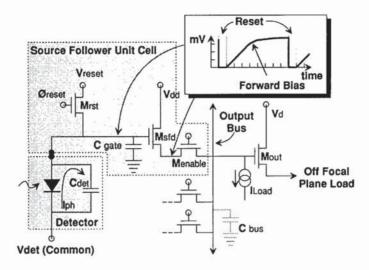

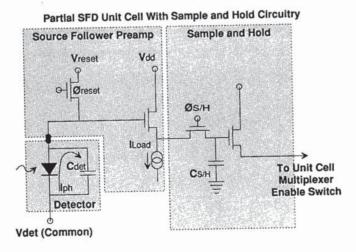

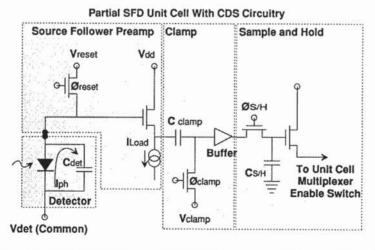

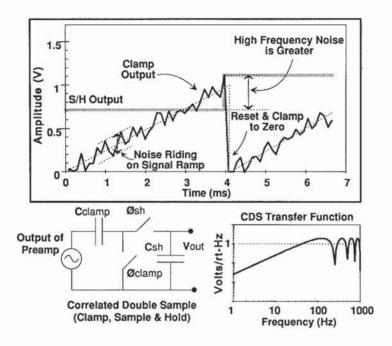

#### 5.6.4 Source Follower per Detector Readout

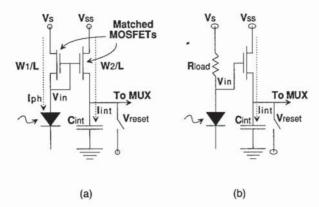

The source follower per detector readout preamplifier (SFD), shown in Fig. 5.14, is similar to the SI but with the addition of a MOSFET for voltage mode output and a reset switch. Only three components, other than the detector,

Fig. 5.14 SFD buffers the voltage resulting from photon charge integration to the video output driver via a source-follower MOSFET configuration. The SFD requires a reset switch on the input node.

are contained in the unit cell; this makes the SFD desirable for applications that require small unit cells.

Photon current is integrated onto the input node stray input capacitance formed by the gate of the source-follower MOSFET, the interconnect, and the detector capacitance. Unlike the SI, the ramping input voltage of the SFD is buffered by the source-follower MOSFET and then multiplexed, via an enable switch, to a common bus prior to the video output buffer. The SFD, which has a voltage mode output, requires no bus amplifier. After the multiplexer read cycle, the input node is reset and the integration cycle begins again. The dynamic range of the SFD is limited in the same way as that of the SI, by the current voltage characteristics of the detector. Charge on the input node creates a voltage at the end of integration according to

$$V_{\rm in} = \frac{I_{\rm det}t_{\rm int}}{C} \quad [V] , \qquad (5.48)$$

where  $I_{\text{det}}$  is the sum of photon and dark currents and C is the stray capacitance on the readout input node. The total excursion of input voltage should not exceed the detector forward bias, or severe signal nonlinearities and additional shot noise can occur. In photovoltaic sensors, this limit can be as low as tens of millivolts or as high as several volts. Additional charge storage can be accommodated by adding an integrated circuit capacitor to the input node.

The buffer MOSFET of the SFD is designed both for low noise and near unity gain. This gain, between the detector node and multiplexer, approaches unity as the MOSFET  $g_m$  and load resistance  $R_l$  are increased:

$$A_{sf} = \frac{1}{1 + (1/g_m R_I)} [V/V] , \qquad (5.49)$$

where  $R_I$  is the combined load resistance presented by the multiplexer, current source load, and video driver input circuits.

MOSFET drain current in the source follower is not driven by noise; rather. it is driven by  $g_m$  requirements and the signal bandwidth of the multiplexer. The current source load for the SFD is located opposite the multiplexer, outside the unit cell, so that power only dissipates in the unit cell MOSFET when it is enabled through the multiplexer onto the video buffer line. The sourcefollower load current must be large enough to drive, or slew, the capacitance of the multiplexer bus. This is covered in detail for the source-follower video driver in Sec. 5.9.

SFD Noise. The SFD is typically utilized in low background applications, such as astronomy. 10 where long integration times accumulate sufficient charge for readout. Gain is fixed by the near-unity gain of the MOSFET source follower and the integration capacitor, which is usually dominated by the detector. In high-sensitivity applications, the detector capacitance must be reduced to very low levels and thus provide high input node gain so that amplifier and multiplexer noise is overcome. Again the kTC noise caused through the reset of the input node must be considered. The major noise sources of the SFD are kTC. MOSFET 1/f, and MOSFET channel thermal noise.

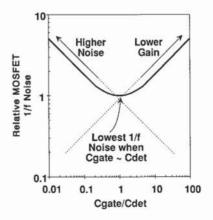

It is important to address 1/f in the input MOSFET because this can often dominate the channel thermal noise to frequencies well above 10 kHz. MOS-FET 1/f noise, as discussed in an earlier section, decreases as the product of the channel width and length (W and L) increases. The product of W and L also drive gate capacitance and, in Fig. 5.15, the relative total 1/f noise is shown as a function of the MOSFET gate-to-detector capacitance ratio. When gate capacitance is much lower than detector capacitance, the photon-to-voltage gain is high but the 1/f noise is also high. When gate capacitance is much larger than detector capacitance, the gain of the SFD is substantially reduced according to Eq. (5.48) and SNR is once again reduced. Optimum gate capacitance occurs at the point where it is equal to the detector capacitance. In practice, the detector capacitance is often sufficiently large such that the MOS-

Fig. 5.15 Minimum MOSFET 1/f noise contribution occurs when gate capacitance is equal to detector capacitance.

FET size, and therefore gate capacitance, cannot be fully optimized due to area limitations in the unit cell.

MOSFET noise at the output of the SFD is the product of MOSFET input referred noise voltage (whether 1/f or channel thermal noise), source-follower gain ( $\sim$ 1), and square root of the equivalent noise bandwidth of the noise,  $\Delta f$ . Periodic sampling through the multiplexer results in the folding of high-frequency noise below the Nyquist frequency of the circuit. In the case of channel thermal noise, the equivalent noise bandwidth,  $\Delta f$  of Eq. (5.10), is the only parameter to optimize for lowering noise.

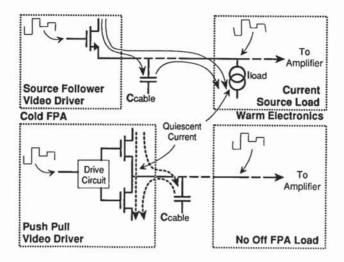

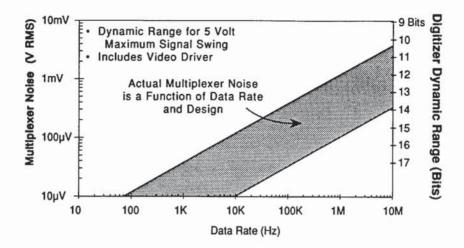

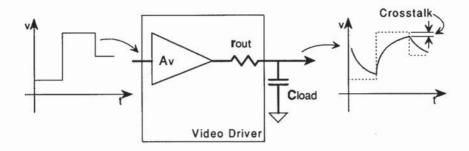

The following discussion addresses the MOSFET channel thermal contribution to source-follower noise. MOSFET 1/f noise, to first order, is geometry and process dependent and not directly dependent on drain current or  $g_m$ . To reduce MOSFET channel thermal noise, the designer's degree of freedom is limited to reducing the noise bandwidth  $\Delta f$  since increasing  $g_m$  of the MOSFET does not have the obvious effect on noise that Eq. (5.10) implies. An increase in  $g_m$ , as a result of increased drain current, W/L ratio, or other means, results in a corresponding increase in the bandwidth  $\Delta f$ , thus canceling any low-noise benefit.