# ECS Transactions, 58 (9) 137-148 (2013) 10.1149/05809.0137ecst ©The Electrochemical Society

# Performance Enhancement Technologies in III-V/Ge MOSFETs

S. Takagi, R. Zhang, S.-H. Kim, M. Yokoyama and M. Takenaka

The University of Tokyo, 7-3-1 Hongo, Bunkyo-ku, Tokyo 113-8656 Japan

CMOS utilizing high mobility III-V/Ge channels on Si substrates is expected to be one of the promising devices for high performance and low power advanced LSIs in the future, because of the enhanced carrier transport properties. However, the device/process/ integration technologies of Ge/III-V n- and pMOSFETs for satisfying requirements of future node MOSFETs have not been established yet. In this paper, we address gate stack and channel engineering for enhancing the MOSFET performance with emphasis on thin EOT and ultrathin body, which are mandatory in the future nodes. As for Ge MOSFETs, GeO<sub>x</sub>/Ge interfaces formed by plasma post oxidation are shown to realize thin EOT, low D<sub>it</sub> and high mobility. By using these HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/GeO<sub>x</sub>/Ge gate stacks, Ge n- and p-MOSFETs with EOT of 0. 76 nm have been demonstrated with high electron (690 cm<sup>2</sup>/Vs) and hole (550 cm<sup>2</sup>/Vs) mobility. As for III-V MOSFETs, ultrathin InAs channels with MOS interface buffer layers are shown to provide high electron mobility for an InAs thickness of 3 nm. By utilizing this channel engineering, 55 nm-L<sub>ch</sub> quantum well channel InAs-OI n-MOSFETs have been demonstrated with superior short channel effect immunity and fairly high on current.

### Introduction

CMOS utilizing high mobility Ge/III-V channels on Si substrates is expected to be one of the promising devices for high performance and low power advanced LSIs in the future [1, 2]. Here, several CMOS structures using III-V/Ge channels can be used. One of the ultimate CMOS can be the co-integration of a III-V nMOSFET and a Ge pMOSFET [1-4]. While Ge or III-V CMOS is also plausible in terms of the simplicity of the process/material integration, the key issues are the realization of high performance III-V pMOSFETs or Ge nMOSFETs. Thus, viable CMOS structures using III-V and/or Ge channels are still strongly dependent on coming progress in the device/process/integration technologies of Ge/III-V n- and pMOSFETs. Also, even in Ge pMOSFETs and III-V nMOSFETs, intensively studied so far, the CMOS technologies for satisfying the requirements of future node MOSFETs have not been established yet. In this paper, we address gate-stack and channel engineering for enhancing the MOSFET performance with emphasis on thin EOT and ultrathin body, which are mandatory in the future nodes.

# **Ge MOSFET Improvement**

The realization of superior Ge MOS interfaces is mandatory for yielding high mobility in inversion layers of Ge MOSFETs. Among a variety of gate insulators and/or interface

control layers on Ge, attention has recently been paid to  $GeO_2/Ge$  interfaces, because of the superior interface properties and resulting high carrier mobility in Ge MOSFETs [7-30]. Particularly, high electron mobility can be obtained only for Ge n-MOSFETs with  $GeO_2/Ge$  interfaces [14-20, 22, 24, 26-30]. The  $GeO_2/Ge$  interfaces with a quite low interface state density can be realized by direct thermal oxidation of Ge substrates [11, 13]. The interface state density systematically decreases as the oxidation temperature increases. As for the capacitors oxidized at 575 °C, we obtained a minimum  $D_{it}$  value of  $1.1 \times 10^{11}$  eV<sup>-1</sup>cm<sup>-2</sup> measured in the range from the valence band edge ( $E_v$ ) to midgap and  $9 \times 10^{10}$  eV<sup>-1</sup>cm<sup>-2</sup> measured in the range from the conduction band edge ( $E_c$ ) to midgap without any interface passivation annealing. Judging from the energy distribution, a minimum value near midgap is expected to be lower than these results. These  $D_{it}$  values are quite low values for Ge MOS interfaces. These superior interface properties of the  $GeO_2/Ge$  interfaces are expected to lead to higher channel mobility. Thus, we have fabricated p- [19, 25] and n-channel [14, 17] MOSFETs with thick  $GeO_2/Ge$  interfaces, formed by thermal oxidation. As a result, we have obtained high electron and hole mobility values of 1020 and 575 cm<sup>2</sup>/Vs, respectively [17, 19].

While recent studies [7, 8, 16, 18, 20, 21] have also revealed that Ge oxide interfacial layers (IL) with high k can provide superior MOS interfaces with low  $D_{it}$ , thinning EOT is still challenging. In order to realize low  $D_{it}$  and thin EOT at the same time, we have proposed a novel IL formation process employing ECR oxygen plasma to form  $GeO_x$  ILs after thin  $Al_2O_3$  ALD [22-26]. In this plasma post-oxidation method, a thin  $GeO_x$  IL is formed by oxidizing a Ge surface beneath a thin ALD  $Al_2O_3$  layer using ECR oxygen plasma exposure. The  $Al_2O_3$  layer serves as a sufficient oxygen barrier that suppresses the growth of unnecessarily thick  $GeO_x$  IL, thanks to its intrinsic oxygen permeability. Also, the  $Al_2O_3$  layer effectively prevents Ge surfaces from receiving the direct exposure of ECR oxygen plasma and any damage during the fabrication processes. In addition, low processing temperature in the ECR plasma oxidation is expected to sufficiently suppress any thermal degradation of the  $GeO_x/Ge$  interface.

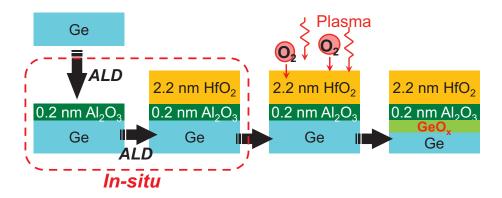

Fig. 1. Proposed  $GeO_x$  IL formation process by using ECR oxygen plasma oxidation through ALD  $HfO_2/Al_2O_3$ .

Also, we have recently demonstrated a revised version of gate insulator formation using ALD HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> stacks for further reducing EOT [27-31]. While the Al<sub>2</sub>O<sub>3</sub>/GeO<sub>x</sub>/Ge gate stacks can realize the superior interfaces, the low permittivity of Al<sub>2</sub>O<sub>3</sub> poses a limitation on thinning EOT around 1 nm, meaning the necessity of HfO<sub>2</sub> for further scaling EOT. Here, the plasma post-oxidation is applied to ALD

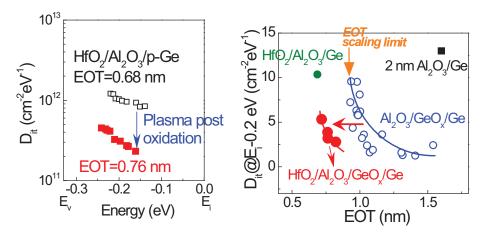

${\rm HfO_2/Al_2O_3/Ge}$  structures. It should be noted here that plasma oxidation of  ${\rm HfO_2/Ge}$  direct stacks provides inferior MOS interface properties with high  ${\rm D_{it}}$ , because of the inter-mixing of  ${\rm HfO_2}$  and  ${\rm GeO_x}$ . Thus, the insertion of ultrathin  ${\rm Al_2O_3}$  films is needed as an inter-diffusion control layer (DCL). The basic process flow is shown in Fig. 1. This ultrathin  ${\rm GeO_x}$  IL is found to effectively reduce  ${\rm D_{it}}$ , as shown in Fig. 2(a). Fig. 2(b) shows  ${\rm D_{it}}$  at  ${\rm E_{i^-}0.2~eV}$  as a function of EOT of  ${\rm HfO_2/Al_2O_3/Ge}$  and  ${\rm Al_2O_3/Ge}$  MOS interfaces with and without  ${\rm GeO_x}$  formed by plasma post oxidation. As a consequence, EOT of the  ${\rm HfO_2/Al_2O_3/GeO_x/Ge}$  gate stacks is scaled down to  $0.7{\sim}0.8$  nm with maintaining  ${\rm D_{it}}$  around  $10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> level.

Fig. 2. (a) Energy distribution of  $D_{it}$  before and after post plasma oxidation for  $HfO_2/Al_2O_3/Ge$  interfaces. (b)  $D_{it}$  at  $E_i$ -0.2 eV as a function of EOT of  $HfO_2/Al_2O_3/Ge$  and  $Al_2O_3/Ge$  MOS interfaces with and without  $GeO_x$  formed by plasma post oxidation.

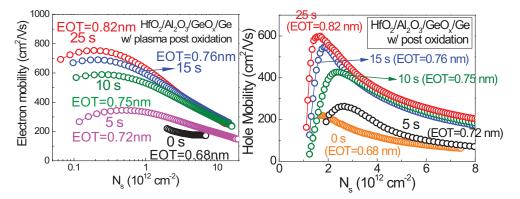

Fig. 3. (a) Electron and (b) hole mobility of the Ge n- and p-MOSFETs with the  $HfO_2$  (2.2 nm)/ $Al_2O_3$  (0.2 nm)/ $GeO_x/Ge$  gate stacks as a parameter of the interfacial  $GeO_x$  thickness.

As a result, n- and p-MOSFETs with HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/GeO<sub>x</sub>/Ge gate stacks exhibit excellent electrical characteristics under EOT of 0.76 nm. This is the first report of Ge n-MOSFETs with EOT less than 1 nm (the thinnest EOT of 0.72 nm). Fig. 3(a) and (b) shows the electron and hole mobility of the Ge n- and p-MOSFETs, respectively, with HfO<sub>2</sub> (2.2 nm)/Al<sub>2</sub>O<sub>3</sub> (0.2 nm)/GeO<sub>x</sub>/Ge gate stacks as a parameter of the interfacial GeO<sub>x</sub> thickness. The Ge p- and n-MOSFETs with HfO<sub>2</sub> (2.2 nm)/Ge and HfO<sub>2</sub> (2.2 nm)/Ge gate stacks show relatively low hole and electron mobility, which

is attributed to the poor qualities of direct  $HfO_2/Ge$  and  $Al_2O_3/Ge$  MOS interfaces. It is found, on the other hand, that the insertion of interfacial  $GeO_x$  and the increase in the thickness significantly enhance the effective mobility. The  $HfO_2$  (2.2 nm)/ $Al_2O_3$  (0.2 nm)/ $GeO_x/Ge$  Ge p- and n-MOSFETs exhibit significantly enhanced mobility, attributed to sufficient passivation of Ge MOS interfaces by the  $GeO_x$  ILs. The electron mobility in the  $HfO_2/Al_2O_3/GeO_x/Ge$  n-MOSFET is comparable to the Si universal electron mobility and approaching the ~20-nm-thick thermal oxidation  $GeO_2/Ge$  n-MOSFET [29, 30]. The hole mobility is much higher than the Si universal one and even higher than that in the thick thermal oxidation  $GeO_2/Ge$  p-MOSFETs is obtained for the  $HfO_2/Al_2O_3/GeO_x/Ge$  p-MOSFET [27, 29, 30].

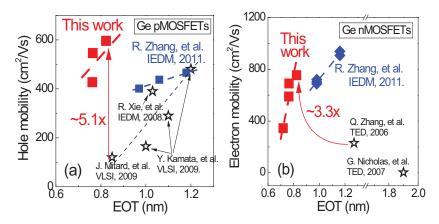

Fig. 4. Peak hole (a) and electron (b) mobility of the Ge p and n-MOSFETs with  $HfO_2/Al_2O_3/GeO_x/Ge$  gate stacks vs. EOT, compared with the Ge MOSFETs with  $Al_2O_3/GeO_x/Ge$  gate stacks and the data reported in other previous studies.

The present and reported data [32-36] of the peak hole and electron mobility of Ge pand n-MOSFETs with EOT of around 1 nm are summarized as a function of EOT in Fig. 4 (a) and (b), respectively. A clear decrease of both the electron and the hole mobility with a decrease in EOT is observed for the values already reported, attributable to the significant degradation of the Ge MOS interfaces. In the Al<sub>2</sub>O<sub>3</sub>/GeO<sub>x</sub> gate stacks fabricated by the plasma post-oxidation method, the degradation of mobility with decreasing EOT is found to be effectively suppressed because of the sufficient passivation of Ge MOS interfaces even in the ultrathin EOT region. However, the EOT scaling is not available beyond 1 nm because of the insufficient permittivity of Al<sub>2</sub>O<sub>3</sub>. In the present HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/GeO<sub>x</sub>/Ge gate stacks, thanks to the higher permittivity of HfO<sub>2</sub> than Al<sub>2</sub>O<sub>3</sub> and the successful formation of GeO<sub>x</sub>/Ge MOS interfaces by employing the plasma post oxidation method and thin Al<sub>2</sub>O<sub>3</sub> DCL, further EOT scaling is realized while maintaining the low Dit Ge MOS interfaces, resulting in the significant improvement of the peak mobility of Ge p- and n-MOSFETs. The peak mobility in the Ge p-MOSFET with EOT of 0.82 nm has been enhanced by 5.1 times over the previously-reported results [33] with similar EOT. On the other hand, since there is no previous data of Ge n-MOSFETs with EOT thinner than 1.3 nm, we cannot compare the peak mobility with the previous results. Even when comparing with the previous data with EOT of 1.3 nm [35], the peak mobility in the Ge n-MOSFET with EOT of 0.82 nm has been enhanced by 3.3 times. A much higher enhancement factor is expected in comparison with the peak mobility of Ge n-MOSFETs with any other MOS interfaces under the same EOT, because the mobility generally tends to decrease with reducing EOT.

## **III-V MOSFET Improvement**

The MOS interface control is more critical for III-V semiconductors than for Ge in terms of obtaining higher effective mobility in MOS channels, because it is well known that MOS interfaces between III-V materials and gate insulators include a large number of interface states and interface defects. Thus, the realization of high quality MOS gate stacks on III-V is of paramount importance. One recent important discovery in III-V MOS interface control is the effectiveness of ALD  $Al_2O_3$  [37-43] on suppression of interface defects. Also, it has been reported that sulfur (S) passivation [44-46] can improve the  $Al_2O_3$ /InGaAs MOS interface properties. We have found that the S passivation, obtained by immersing InGaAs epitaxial surfaces into (NH<sub>4</sub>)<sub>2</sub>S solutions, can also improve the effective electron mobility in InGaAs n-MOSFETs [46]. It has been found that  $\mu_{eff}$  can be improved by using the (111)A surface and the (NH<sub>4</sub>)<sub>2</sub>S treatment, though the physical origin of this mobility improvement has not been fully understood yet.

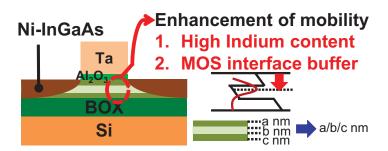

Fig. 5. Schematic image of the device structure and channel engineering for In<sub>x</sub>Ga<sub>1-x</sub>As-OI MOSFETs.

Another critical factor for the electron mobility reduction in InGaAs MOSFETs is the influence of the ultrathin body channels, which are mandatory for short channel MOSFETs. It has been reported that ultrathin Si channels severely reduce the channel mobility, because of increased body thickness fluctuation scattering [47, 48]. It is also found for III-V MOSFETs that, when the body thickness,  $T_{body}$ , is less than 10 nm, the mobility significantly decreases with a decrease in  $T_{body}$ , which is consistent with the expectation in the mobility limited by body thickness fluctuation scattering [49-52]. Therefore, we have introduced two kinds of channel engineering [53-56]. Fig. 5 shows the schematic image of the device structure and channel engineering for In<sub>x</sub>Ga<sub>1-x</sub>As-OI MOSFETs. One is the higher In content (InAs) channels and the other is the insertion of a MOS interface buffer layer at both the bottom and the top of a channel layer using InGaAs with a low In content, which has a higher band gap than that of the channel InGaAs, to distance the channel carriers from the MOS interface. The lower-In-content MOS buffer layers are expected to reduce MOS interface Coulomb scattering. In addition, the thickness fluctuation of the high-In content channel layers can be mitigated, because both the lower- and higher-In content InGaAs channels are epitaxially grown successively, while the thickness of the single layer InGaAs-OI channels are formed by etching processes during direct wafer bonding (DWB). Also, higher In content (InAs) channels are expected to provide higher phonon-limited mobility.

In order to realize this device structure, In<sub>x</sub>Ga<sub>1-x</sub>As-OI structures on Si were fabricated by DWB. The process details are shown in [49]. Also, MOSFETs with Ni-InGaAs metal source/drain (S/D) were fabricated on the In<sub>x</sub>Ga<sub>1-x</sub>As-OI substrates. The III-V-OI wafers were cleaned by acetone, 9.5 % NH<sub>4</sub>OH, and 0.6 % (NH<sub>4</sub>)<sub>2</sub>S solutions for 1, 1, and 10 min, respectively. Then, 10-nm-thick Al<sub>2</sub>O<sub>3</sub> was deposited at 200 °C by ALD using Al(CH<sub>3</sub>)<sub>3</sub> and H<sub>2</sub>O as the liquid sources. Subsequently, Ta gate deposition by sputtering and gate patterning were carried out. Post-metal-annealing was carried out at 350 °C for 10 sec in N<sub>2</sub> ambient. After that, 20 nm Ni for S/D was deposited by electron beam evaporation with lift off process and rapid-thermal-annealing was carried out at 250 °C in N<sub>2</sub> ambient to form the Ni-InGaAs S/D regions. Next, unreacted Ni was removed by a 6 % HCl solution with high etching selectivity between Ni and the formed Ni-InGaAs alloy. Finally, Al for pad electrodes and back contact were evaporated.

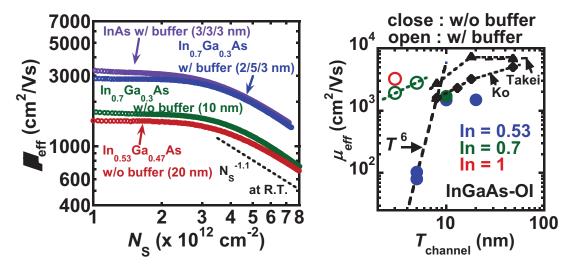

Fig. 6. (a)  $N_s$  dependence of effective electron mobility at room temperature for InGaAs-based ultrathin body MOSFETs. (b) Comparison of the effective electron mobility of  $In_xGa_{1-x}As$ -OI MOSFETs with that of other studies on InAs-OI MOSFETs [50, 52] as a function of  $T_{channel}$ .

The effective electron mobility ( $\mu_{eff}$ ) characteristics of  $In_xGa_{1-x}As$ -OI MOSFETs with a  $T_{body}$  between 10-20 nm at room temperature (R.T.) are shown in Fig. 6(a). It is found that the  $In_xGa_{1-x}As$  channels with higher In content show higher  $\mu_{eff}$  even though the higher In content channel has thinner  $T_{body}$ . Also, MOSFETs with a buffer layer shows higher  $\mu_{eff}$ . The InAs-OI MOSFETs with  $T_{channel}$  of 3 nm exhibit high peak mobility of 3180 cm<sup>2</sup>/Vs. Fig. 6(b) shows the comparison in  $\mu_{eff}$  of  $In_xGa_{1-x}As$  MOSFETs with that of other studies as a function of  $T_{channel}$ . The data from the other studies of InAs-OI MOSFETs [50, 52] are also shown. It is found that  $\mu_{eff}$  of InGaAs-OI MOSFETs in this work is higher than the previous data taken from the other studies exploring ETB InAs MOSFETs [50-52], attributable to the existence of the MOS interface buffer layer.

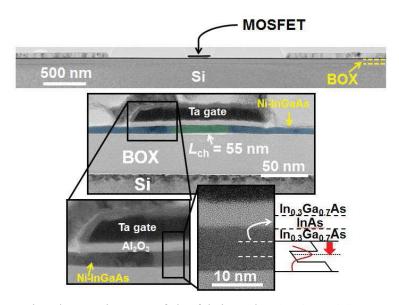

By utilizing this device structure, we have also demonstrated operation of 55-nm-L<sub>ch</sub> MOSFETs on Si [55, 57]. In order to realize short channel devices, EB lithography of the gate electrode patterning and Ni encroachment were employed. In Ni-InGaAs metal S/D formation, Ni diffused toward the lateral direction of the channels by a diffusion length of

around 50 nm during 1 min. RTA. This encroachment allows us to fabricate the deeply-scaled MOSFETs under the several hundred nm gate patterns. The cross-sectional transmission electron microscope (TEM) images of a fabricated MOSFET with the buffer layer (3/3/3 nm) are shown in Fig. 7. It can be seen that ETB InAs-OI MOSFETs were fabricated on a Si substrate with the metal S/D structures. The large area TEM image shows that the formed InGaAs-OI and the buried oxide (BOX) layer have good uniformity. The laterally-diffused Ni-InGaAs layer was observed and, as a result, the effective  $L_{\rm ch}$  was estimated to be 55 nm with a defined gate length of 160 nm.

Fig. 7. Cross-sectional TEM images of the fabricated InAs-OI MOSFETs with  $L_{ch}$  of 55 nm and  $T_{body}$  of 3/3/3 nm.

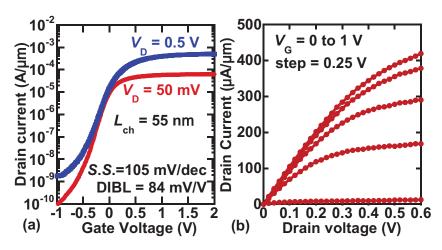

Fig. 8. (a)  $I_D$ - $V_G$  and (b)  $I_D$ - $V_D$  characteristics of InAs-OI MOSFETs with  $T_{body}$  of 3/3/3 nm and  $T_{ox} = 6$  nm.

The  $I_D$ - $V_G$  and  $I_D$ - $V_D$  characteristics of the InAs-OI MOSFET with  $L_{\rm ch}$  of 55 nm,  $T_{\rm body}$  of 3/3/3 nm and Al<sub>2</sub>O<sub>3</sub> gate dielectric thickness ( $T_{\rm ox}$ ) of 6 nm are shown in Figs. 8(a) and 8(b), respectively. The device shows good transfer and output characteristics with small DIBL in spite of quite thick EOT of around 3.5 nm. High  $I_{\rm on}$  of 278  $\mu$ A/ $\mu$ m is obtained at

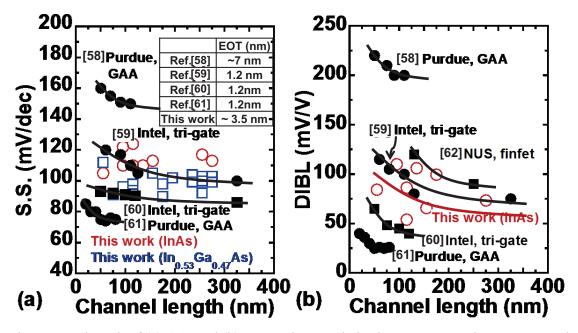

$V_{\rm dd}$  of 0.5 V. This  $I_{\rm on}$  value of the present device is comparable to that of the Tri-gate MOSFETs [58-62], reported so far, in spite of the ETB planar structure. This result demonstrates the operation of ETB InAs-OI MOSFETs on Si substrates with a  $L_{\rm ch}$  region of sub-100 nm. Figs. 9(a) and 9(b) show the *S.S.* and DIBL benchmark comparing those of the present InGaAs-OI MOSFETs with the recent results of the III-V 3-D FETs [58-62]. The present In<sub>x</sub>Ga<sub>1-x</sub>As-OI MOSFETs show comparable or better electrostatic characteristics against the 3-D Tri-gate FET or gate-all-around (GAA) FETs [58-62], even though quite thick EOT and the planar structure have been used.

Fig. 9. Benchmark of (a) S.S. and (b) DIBL characteristics between several 3-D FETs and the present devices.

However, the above devices still suffered from fairly high parasitic resistance due to high contact resistance between contact metals and Ni-InGaAs. Recently, we present 20-nm-channel length ( $L_{ch}$ ) high performance InAs-on-insulator (-OI) MOSFETs on Si substrates with Ni-InGaAs metal source/drain (S/D) employing a new contact resistance reduction technology [63]. These devices provide high maximum  $I_{on}$  and maximum transconductance ( $G_m$ ) of 2.38 mA/ $\mu$ m and 1.95 mS/ $\mu$ m at  $V_D$  of 0.5 V. This high performance is attributable to the low S/D parasitic resistance, which was realized by a cleaning process of Ni-InGaAs surfaces before pad electrode deposition as well as increase in In content in the channel layer. Furthermore, it has been found that the interface resistance between Ni-InGaAs and InGaAs channels can be reduced down to 50  $\Omega$ : $\mu$ m by increasing In content in the channel layers.

## **Conclusions**

In this paper, we address key issues to enhance the performance of III-V/Ge MOSFETs. As for Ge MOSFETs, the formation of the superior gate stacks is a key issue. It was shown that ECR plasma post oxidation through  $HfO_2/Al_2O_3$  is quite effective in realizing Ge gate stacks with EOT less than 1 nm with low  $D_{it}$  and resulting high electron

and hole mobility in Ge MOSFETs. Record high mobility Ge n- and p-MOSFETs with EOT of 0. 76 nm have been demonstrated by using HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/GeO<sub>x</sub>/Ge gate stacks. As for InGaAs MOSFETs, the channel structure engineering for mitigating the mobility reduction mechanisms such as channel thickness fluctuation scattering and MOS interface Coulomb scattering is a key issue. We have proposed MOS interface buffer quantum well channels by using InGaAs/InAs/InGaAs-On-Insulator structures. It was shown that significant electron mobility enhancement is observed down to 3 nm of InAs channels. By utilizing this engineering, we have realized 55-nm-L<sub>g</sub> InGaAs-OI MOSFETs with Ni-InGaAs S/D on Si substrates, realized by direct wafer bonding between InGaAs and Si substrates with ultrathin Al<sub>2</sub>O<sub>3</sub> buried oxides (BOX). The superior short channel immunity and fairly high I<sub>on</sub> have been obtained.

# Acknowledgments

This work was partly supported by a Grant-in-Aid for Scientific Research (No. 23246058) from MEXT and Research and Development Program for Innovative Energy Efficiency Technology from NEDO. The authors would like to thank Dr. M. Yokoyama, Dr. R. Zhang, S.-H. Kim and R. Suzuki in the University of Tokyo, Dr. N. Taoka in Nagoya University, Drs. T. Yasuda, T. Maeda, W. Jevasuwan, N. Miyata, Y. Urabe and H. Takagi in AIST, Drs. M. Hata, T. Osada, O. Ichikawa, and N. Fukuhara in Sumitomo Chemical, and Dr. H. Yokoyama in NTT for their collaborations.

### References

- 1. International Technology Roadmap for Semiconductors (ITRS) 2012 Edition, http://www.itrs.net/Links/2012ITRS/Home2012.htm

- 2. S. Takagi, T. Tezuka, T. Irisawa, S. Nakaharai, T. Numata, K. Usuda, N. Sugiyama, M. Shichijo, R. Nakane, S. Sugahara, *Solid-State Electron.*, **51**, 526 (2007).

- 3. S. Takagi, T. Irisawa, T. Tezuka, T. Numata, S. Nakaharai, N. Hirashita, Y. Moriyama, K. Usuda, E. Toyoda, S. Dissanayake, M. Shichijo, R. Nakane, S. Sugahara, M. Takenaka, and N. Sugiyama, *IEEE Trans. Electron Devices*, **55**, 21, (2008).

- 4. S. Takagi and M. Takenaka, IEEE Symp. on VLSI Technol., 147 (2010).

- S. Takagi, T. Maeda, N. Taoka, M. Nishizawa, Y. Morita, K. Ikeda, Y. Yamashita, M. Nishikawa, H. Kumagai, R. Nakane, S. Sugahara and N. Sugiyama, *Microelectron. Eng.*, 84, 2314 (2007).

- 6. Y. Fukuda, T. Ueno, S. Hirono, and S. Hashimoto, *Jpn. J. Appl. Phys.*, **44**, Part 1, p. 6981 (2005).

- 7. A. Delabie, F. Bellenger, M. Houssa, T. Conard, S. V. Elshocht, M. Caymax, M. M. Heyns, and M. Meuris, *Appl. Phys. Lett.*, **91**, 082904 (2007).

- 8. T. Takahashi, T. Nishimura, L. Chen, S. Sakata, K. Kita and A. Toriumi, *IEEE Int. Electron Device Meeting*, p. 697 (2007).

- 9. D. Kuzum, A. J. Pethe, T. Krishnamohan, Y. Oshima, Y. Sun, J. P. McVittie, P. A. Pianetta, P. C. McIntyre and K. C. Saraswat, *IEEE Int. Electron Device Meeting*, p. 723 (2007).

- 10. K. Kita, S. Suzuki, H. Nomura, T. Takahashi, T. Nishimura, and A. Toriumi, *Jpn. J. Appl. Phys.*, **47**, 2349 (2008).

- 11. H. Matsubara, T. Sasada, M. Takenaka and S. Takagi, *Appl. Phys. Lett.*, **93**, 032104 (2008).

- 12. Y. Nakakita, R. Nakane, T. Sasada, H. Matsubara, M. Takenaka and S. Takagi, *IEEE Int. Electron Device Meeting*, (2008) p. 877

- 13. T. Sasada, Y. Nakakita, M. Takenaka and S. Takagi, *J. Appl. Phys.*, **106**, 073716 (2009).

- 14. K. Morii, T. Iwasaki, R. Nakane, M. Takenaka and S. Takagi, *IEEE Int. Electron Device Meeting*, 681 (2009).

- 15. C. H. Lee, T. Nishimura, N. Saido, K. Nagashio, K. Kita and A. Toriumi, *IEEE Int. Electron Device Meeting*, 457 (2009).

- 16. T. Nishimura, C. H. Lee, S. K. Wang, T. Tabata, K. Kita, K. Nagashio and A. Toriumi, *IEEE Symp. on VLSI Technol.*, 209 (2010).

- 17. K. Morii, T. Iwasaki, R. Nakane, M. Takenaka, and S. Takagi, *IEEE Electron Device Lett.*, **31**, 1092 (2010).

- 18. C. H. Lee, T. Nishimura, T. Tabata, S. K. Wang, K. Nagashio, K. Kita, and A. Toriumi, *IEEE Int. Electron Device Meeting*, 416 (2010).

- 19. Y. Nakakita, R. Nakakne, T. Sasada, M. Takenaka and S. Takagi, *Jpn. J. Appl. Phys.*, **50**, 010109 (2011).

- 20. C. H. Lee, T. Nishimura, K. Nagashio, K. Kita, and A. Toriumi, *IEEE Tran. Electron Devices*, **58**, p. 1295(2011).

- 21. R. Zhang, T. Iwasaki, N. Taoka, M. Takenaka and S. Takagi, *J. Electrochem. Soc.* **158** G178 (2011).

- 22. R. Zhang, T. Iwasaki, N. Taoka, M. Takenaka and S. Takagi, *Appl. Phys. Lett.*, **98**, 112902 (2011).

- 23. R. Zhang, T. Iwasaki, N. Taoka, M. Takenaka and S. Takagi, *IEEE Symp. on VLSI Technol.*, 56 (2011).

- 24. R. Zhang, T. Iwasaki, N. Taoka, M. Takenaka and S. Takagi, *Microelectron. Eng.*, **88**, 1533 (2011).

- 25. R. Zhang, N. Taoka, P. Huang, M. Takenaka and S. Takagi, *Tech. Dig. IEEE Int. Electron Device Meeting*, p. 642 (2011).

- 26. R. Zhang, T. Iwasaki, N. Taoka, M. Takenaka and S. Takagi, *IEEE Trans. Electron Devices*, **59**, 335 (2012).

- 27. R. Zhang, P. C. Huang, N. Taoka, M. Takenaka and S. Takagi, *IEEE Symp. on VLSI Technol.*, p. 161 (2012).

- 28. R. Zhang, P.-C. Huang, J.-C. Lin, M. Takenaka and S. Takagi, *Tech. Dig. IEEE Int. Electron Device Meeting*, p. 371 (2012).

- 29. S. Takagi, R. Zhang, S.-H. Kim, N. Taoka, M. Yokoyama, J.-K. Suh, R. Suzuki, Y. Asakura, C. Zota and M. Takenaka, *Tech. Dig. IEEE Int. Electron Device Meeting*, p. 505 (2012).

- 30. R. Zhang, P.-C. Huang, J.-C. Lin, N. Taoka, M. Takenaka and S. Takagi, *IEEE Trans. Electron Devices*, **60**, 927 (2013).

- 31. R. Zhang, J-C. Lin, X. Yu, M. Takenaka and S. Takagi, *IEEE Symp. on VLSI Technol.*, p. (2013).

- 32. R. Xie, T. H. Phung, W. He, Z. Sun, M. Yu, Z. Cheng, and C. Zhu, *Tech. Dig. IEEE Int. Electron Device Meeting*, p. 393 (2008).

- 33. J. Mitard, C. Shea, B. DeJaeger, A. Pristera, G. Wang, M. Houssa, G. Eneman, G. Hellings, W-E. Wang, J. C. Lin, F. E. Leys, R. Loo, G. Winderickx, E. Vrancken, A. Stesmans, K. De Meyer, M. Caymax, L. Pantisano, M. Meuris, and M. Heyns, *IEEE Symp. on VLSI Technol.*, p. 82 (2009).

- 34. Y. Kamata, K. Ikeda, Y. Kamimuta, and T. Tezuka, *IEEE Symp. on VLSI Technol.*, p. 211 (2009).

- 35. Q. Zhang, J. Huang, N. Wu, G. Chen, M. Hong, L. K. Bera, and C. Zhu, *IEEE Electron Device Lett.* **27**, 728 (2006).

- G. Nicholas, D. P. Brunco, A. Dimoulas, J. Van Steenbergen, F. Bellenger, M. Houssa, M. Caymax, M. Meuris, Y. Panayiotatos, and A. Sotiropoulos, *IEEE Trans. Electron Devices* 54, 1425 (2007).

- 37. M. M. Frank, G. D. Wilk, D. Starodub, T. Gustafsson, E. Garfunkel, Y. J. Chabal, J. Grazul, and D. A. Muller, *Appl. Phys. Lett.*, **86**, 152904 (2005).

- 38. M. L. Huang, Y. C. Chang, C. H. Chang, Y. J. Lee, P. Chang, J. Kwo, T. B. Wu, and M. Hong, *Appl. Phys. Lett.*, **87**, 252104 (2005).

- 39. C.-H. Chang, Y.-K. Chiou, Y.-C. Chang, K.-Y. Lee, T.-D. Lin, T.-B. Wu, M. Hong and J. Kwo, *Appl. Phys. Lett.* **89**, 242911 (2006).

- 40. Y. Xuan, Y. Q. Wu and P. D. Ye, *IEEE Electron Device Lett.*, **29**, 294 (2008).

- 41. M. Egard, L. Ohlsson, B. M. Borg, F. Lenrick, R. Wallenberg, L.-E. Wernersson, and E. Lind, Tech. Dig. *IEEE Int. Electron Device Meeting*, p. 303 (2011).

- 42. Y. Yonai, T. Kanazawa, S. Ikeda, and Y. Miyamoto, Tech. Dig. *IEEE Int. Electron Device Meeting*, p. 307 (2011).

- 43. R. Suzuki, N. Taoka, S. Lee, S. H. Kim, T.Hoshii, M. Yokoyama, T. Yasuda, W. Jevasuwan, T. Maeda, O. Ichikawa, N. Fukuhara, M. Hata, M. Takenaka and S. Takagi, *Appl. Phys. Lett.*, **100**, 132906 (2012).

- 44. Y. Xuan, Y. Q. Wu, T. Shen, T. Yang and P. D. Ye, *IEEE Int. Electron Device Meeting*, 637 (2007).

- 45. É. O'Connor, B. Brennan, V. Djara, K. Cherkaoui, S. Monaghan, S. B. Newcomb, R. Contreras, M. Milojevic, G. Hughes, M. E. Pemble, R. M. Wallace, and P. K. Hurley, *J. Appl. Phys.* **109**, 024101 (2011).

- 46. Y. Urabe, N. Miyata, H. Ishii, T. Itatani, T. Maeda, T. Yasuda, H. Yamada, N. Fukuhara, M. Hata, M. Yokoyama, N. Taoka, M. Takenaka and S. Takagi, *IEEE Int. Electron Device Meeting*, p. 142 (2010).

- 47. K. Uchida and S. Takagi, Appl. Phys. Lett. 82, 2916 (2003).

- 48. K. Uchida, J. Koga, and S. Takagi, *J. Appl. Phys.* **102**, 074510 (2007).

- 49. S. -H. Kim, M. Yokoyama, N. Taoka, R. Iida, S. Lee, R. Nakane, Y. Urabe, N. Miyata, T. Yasuda, H. Yamada, N. Fukuhara, M. Hata, M. Takenaka, and S. Takagi, *Appl. Phys. Express* 4, 024201 (2011).

- H. Ko, K. Takei, R. Kapadia, S. Chuang, H. Fang, P. W. Leu, K. Ganapathi, E. Plis, H. S. Kim, S.-Y. Chen, M. Madsen, A. C. Ford, Y.-L. Chueh, S. Krishna, S. Salahuddin, and A. Javey, *Nature* 468, 286 (2010).

- 51. K. Takei, S. Chuang, H. Fang, R. kapadia, C. -H. Liu, J. Nah, H. S. Kim, E. Plis, S. Krishna, Y. -L. Chueh, and A. Javey, *Appl. Phys. Lett.* **99**, 103507 (2011).

- 52. K. Takei, H. Fang, S. B. Kumar, R. Kapadia, Q. Gao, M. Madsen, H. S. Kim, C. -H. Liu, Y. -L. Chueh, E. plis, S. Krishna, H. A. Bechtel, J. Guo, and A. Javey, *Nano Lett.* 11, 5008 (2011).

- 53. S. H. Kim, M. Yokoyama, N. Taoka, R. Nakane, T. Yasuda, M. Ichikawa, N. Fukuhara, M. Hata, M. Takenaka and S. Takagi, *IEEE Int. Electron Device Meeting*, p. 311 (2011).

- 54. S.-H. Kim, M. Yokoyama, N. Taoka, R. Iida, S.-H. Lee, R. Nakane, Y. Urabe, N. Miyata, T. Yasuda, H. Yamada, N. Fukuhara, M. Hata, M. Takenaka and S. Takagi, *Appl. Phys. Exp.* **5**, 014201 (2012).

### ECS Transactions, 58 (9) 137-148 (2013)

- 55. S. -H. Kim, M. Yokoyama, N. Taoka, R. Nakane, T. Yasuda, O. Ichikawa, N. Fukuhara, M. Hata, M. Takenaka and S. Takagi, *IEEE Symp. on VLSI Technol.*, p. 177 (2012).

- 56. S.-H. Kim, M. Yokoyama, N. Taoka, R. Nakane, T. Yasuda, O. Ichikawa, N. Fukuhara, M. Hata, M. Takenaka and S. Takagi, *IEEE Trans. on Nanotechnology*, **12**, p. 621 (2013).

- 57. S.-H. Kim, M. Yokoyama, N. Taoka, R. Nakane, T. Yasuda, O. Ichikawa, N. Fukuhara, M. Hata, M. Takenaka and S. Takagi, published in *IEEE Trans. Electron Devices* **60** (2013).

- 58. J. J. Gu, Y. Q. Liu, Y. Q. Wu, R. Colby, R. G. Gordon, and P. D. Ye, *IEEE Int. Electron Device Meeting*, p. 769 (2011).

- M. Radosavljevic, G. Dewey, J. M. Fastenau, J. Kavalieros, R. Kotlyar, B. Chu-Kung, W. K. Liu, D. Lubyshev, M. Metz, K. Millard, N. Mukherjee, L. Pan, R. Pillarisetty, W. Rachmady, U. Shah, and R. Chau, *IEEE Int. Electron Device Meeting*, p.126 (2010).

- M. Radosavljevic, G. Dewey, D. Basu, J. Boardman, B. Chu-Kung, J. M. Fastenau, S. Kabehie, J. Kavalieros, V. Le, W. K. Liu, M Metz, K. Millard, N. Mukherjee, L. Pan, R. Pillarisetty, W. Rachmady, U. Shah, H. W. Then, and R. Chau, *IEEE Int. Electron Device Meeting*, p. 765 (2011).

- 61. J. J. Gu, X. W. Wang, H. Wu, J. Shao, A. T. Neal, M. J. Manfra, R. G. Gordon, and P. D. Ye, *IEEE Int. Electron Device Meeting*, p. 633 (2012).

- 62. H. -C. Chin, X. Gong, L. Wang, H. K. Lee, L. Shi, and Y. -C. Yeo, *IEEE Electron Device Lett.* 32, p. 146 (2011).

- 63. S. H. Kim, M. Yokoyama, R. Nakane, O. Ichikawa, T. Osada, M. Hata, M. Takenaka and S. Takagi, *IEEE Symp. on VLSI Technol.* (2013).