# ELECTRICAL PROPERTIES OF HAFNIUM OXIDE GATE DIELECTRIC DEPOSITED BY PLASMA ENHANCED CHEMICAL VAPOR DEPOSITION

## KYU-JEONG CHOI, WOONG-CHUL SHIN, JONG-BONG PARK, AND SOON-GIL YOON

Department of Materials Engineering, Chungnam National University, 220 Gung-Dong, Yuseong-Gu, Daejeon, 305-764 Korea

(Received March 14, 2001; In final form August 20, 2001)

Hafnium oxide thin films were deposited at 300 °C on p-Si (100) substrates by plasma enhanced chemical vapor deposition (PECVD). The gate dielectric formed by PECVD was HfO<sub>2</sub>/SiO<sub>2</sub>/Si structure. The thickness of the HfO<sub>2</sub> thin films decreases with increasing RTA temperature because of its high density. The Pt/HfO<sub>2</sub>/SiO<sub>2</sub>/Si structure showed accumulation, depletion and inversion. After the RTA treatment, the capacitances of the Pt/HfO<sub>2</sub>/SiO<sub>2</sub>/Si structures were increased because, the thickness of HfO<sub>2</sub> thin film decreased. The counterclockwise hysteresis of the C-V curve is believed to be due to charge trapping at the negative gate bias. Hysteresis of as-deposited gate dielectric is quite large, but rapidly decreases with increasing RTA temperature. The increase in leakage current density by the O<sub>2</sub> anneal seems to be related to the grain growth of the HfO<sub>2</sub> thin film. After forming gas annealing, the electrical properties did not largely improve.

Keywords: PECVD; Gate dielectrics; HfO2

#### INTRODUCTION

Considering the technology roadmap, and equivalent oxide thickness of less than  $15\,\text{Å}$  will be necessary to meet the requirements for  $0.1\,\mu\text{m}$  technology. As the  $\text{SiO}_2$  thickness scales below 20 Å the gate leakage of the metal oxide semiconductor field effect transistor (MOSFET) becomes unacceptably high due to excessive tunneling current. For  $\text{SiO}_2$  layers, direct tunneling of electrons becomes quite important for layers thinner than  $15\,\text{Å}$ , leading to a leakage current at operating voltage of  $1\times 10\,\text{A/cm}^2$ .

Since technology roadmaps predict the need for 15 Å and below gate dielectrics in the near future, many high-k gate dielectric materials, such as HfO<sub>2</sub>, ZrO<sub>2</sub>, La<sub>2</sub>O<sub>3</sub> and their silicates have been studied as alternatives for SiO<sub>2</sub>. [3-12] HfO<sub>2</sub>, especially, has desirable properties such as high dielectric constant (~30), high heat of formation (271 kcal/mol), [13] and relatively large band gap (5.86 eV). [14] HfO<sub>2</sub> also is very resistive to impurity diffusion and intermixing at the interface because of its high density (9.68 g/cm). [14] These properties make HfO<sub>2</sub> one of the most promising candidates for alternative gate dielectric application.

So far, HfO<sub>2</sub> thin films have been prepared by sputtering<sup>[3, 5-6]</sup> and thermal chemical vapor deposition (CVD). <sup>[4]</sup> The thermal CVD method has actually produced pertinent HfO<sub>2</sub> thin film quality at a temperature around 500°C using Hf[OC(CH<sub>3</sub>)<sub>3</sub>]<sub>4</sub>. It should be noted that a PECVD method of deposited HfO<sub>2</sub> thin films has not been reported. Compared with thermal CVD method, the PECVD technique of formation of the thin films has some other advantages, such as the low deposition temperature and control of deposition.

In this study, HfO<sub>2</sub> gate dielectric thin films were deposited by plasma enhanced chemical vapor deposition (PECVD). The physical and electrical properties were evaluated as a function of annealing temperature and ambient.

#### EXPERIMENTAL PROCEDURE

The HfO<sub>2</sub> films were deposited on p-type Si (100) substrates by PECVD in O<sub>2</sub> ambient at 300°C. The Hf[OC(CH<sub>3</sub>)<sub>3</sub>]<sub>4</sub> was vaporized in the bubbler at 30°C and was carried to the reactor using argon as the carrier gas. The chamber was maintained at 1 Torr during deposition. The HfO2 deposition parameters were as follows: the Ar flow rate was 100 standard cubic centimeters per minute (sccm), the O2 flow rate was 100 sccm, and the radio frequency (rf) power was 40 W. These samples were transferred to the RTA chamber and annealed at 600 ℃~ 800 ℃ for 3 min in O2 and N2 ambient. After RTA, a Pt electrode to measure electrical properties was sputter deposited, patterned, and etched using aqua regia (1HNO<sub>3</sub>:9HCl:10H<sub>2</sub>O) at 100°C. The capacitor area for the MOS (Pt/HfO<sub>2</sub>/SiO<sub>2</sub>/Si) structure was 3 × 10<sup>-4</sup> cm<sup>2</sup>. After gate patterning, the backside of the sample was etched to expose the silicon substrate and metallized with Pt to reduce the series resistance. Forming gas annealing (FGA) was performed at 350°C for 30 min in 4%  $H_2$ .

The physical thickness of HfO<sub>2</sub> thin film was measured using high-resolution transmission electron microscopy (TEM, CM20T/STEM, Philips). Carbon contamination of HfO<sub>2</sub> thin film was analyzed using auger electron spectroscopy (AES, VG Scientific Microlab 310-D). The capacitance-voltage (C-V) curves of the MOS capacitor were measured using a HP4194A impedance/gain-phase analyzer. Capacitance equivalent oxide thickness (CET) was extracted from the accumulation capacitance at 1 MHz and quantum mechanical correction was not applied. A Keithley 617 programmable electrometer was used for leakage current density measurements.

#### RESULTS AND DISSCUSION

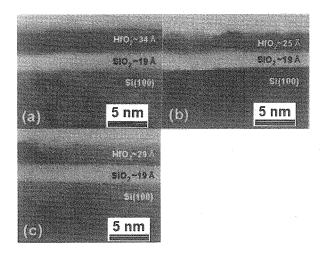

Figure 1 shows the high-resolution transmission electron microscopy (HR TEM) image of the HfO<sub>2</sub> thin films. This images clearly shows the formation between HfO<sub>2</sub> thin films and Si substrate of the amorphous interfacial layer

having a thickness of  $19\,\text{Å}$  because, at the initial stage of deposition,  $S_{1}$  substrate was exposed at  $O_{2}$  ambient. The thickness of the interfacial layer did not change after RTA. The thickness of the  $HfO_{2}$  thin films decreases with increasing RTA temperature because of its high density.

FIGURE 1 HR TEM images of  $HfO_2/SiO_2/Si$  structure (a) as-deposited and annealed in (b)  $O_2$  and (c)  $N_2$  ambient at  $800\,^{\circ}\text{C}$  for 3 minute.

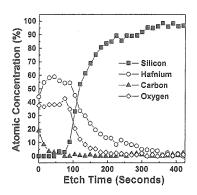

FIGURE 2 AES depth profile of  $HfO_2/SiO_2/Si$  structure before RTA

To analyze the carbon contamination of the HfO<sub>2</sub>/SiO<sub>2</sub>/Si structure, AES depth profiling was performed. Figure 2 show the AES depth profile of the HfO<sub>2</sub>/SiO<sub>2</sub>/Si structure before RTA. The AES depth profile shows the presence of approximately 20 at. % carbon at surface. While some carbon is likely residual from the metalorganic deposition process, carbon contamination is also expected from the in-air sample transfer to the analysis chamber. The carbon content of the films was below the detection limit after RTA.

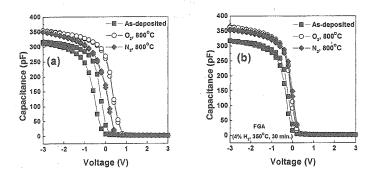

High frequency (1 MHz) C-V curves of Pt/HfO<sub>2</sub>/SiO<sub>2</sub>/Si (a) before FGA and (b) after FGA are shown in figure 3. The Pt/HfO<sub>2</sub>/SiO<sub>2</sub>/Si structure showed accumulation, depletion and inversion. After the RTA treatment, the capacitances of Pt/HfO<sub>2</sub>/SiO<sub>2</sub>/Si structures were increased because, the thickness of HfO<sub>2</sub> thin film decreased. In Fig. 3(a), large flatband voltage shifts were observed after RTA. We speculate that the HfO<sub>2</sub> thin film contain positive charges. After RTA, the flatband shifts toward the positive gate voltage. In addition, it is thought that the HfO<sub>2</sub>/SiO<sub>2</sub>/Si structure annealed in O<sub>2</sub> had more negative charges than the HfO<sub>2</sub>/SiO<sub>2</sub>/Si structure annealed in N<sub>2</sub>, thus showed larger flatband voltage shift. After FGA, the capacitance and flatband voltage shift slightly improved.

FIGURE 3 High frequency (1 MHz) C-V curves of Pt/HfO<sub>2</sub>/SiO<sub>2</sub>/Si structure (a) before forming gas annealing (FGA) and (b) after FGA. The capacitor area is 3x10<sup>-4</sup>cm.

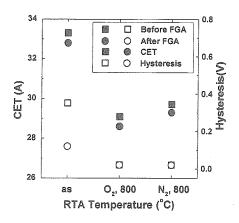

Figure 4 shows the capacitance equivalent oxide thickness (CET) and hysteresis of  $Pt/HfO_2/SiO_2/Si$  structure. The CET of the  $HfO_2$  thin films annealed at  $800\,^{\circ}$ C in  $O_2$  ambient is about  $29\,^{\circ}$ A. The counterclockwise hysteresis of C-V curve is believed to be due to charge trapping at the negative gate bias. The hysteresis of as-deposited gate dielectric is quite large, but rapidly decreases with increasing RTA temperature for 3 minutes. The hysteresis in samples annealed at  $800\,^{\circ}$ C in  $O_2$  and  $O_2$  was reduced to a negligible level of about 20 mV. After FGA, the CET slightly decreased and the hysteresis did not change.

FIGURE 4 Capacitance equivalent oxide thickness (CET) and hysteresis of Pt/HfO<sub>2</sub>/SiO<sub>2</sub>/Si structure before FGA and after FGA. The capacitor area is  $3\times10^{-4}$ cm².

Interface trap density can be measured by a high frequency method developed by Terman. <sup>15</sup> Interface trap density of the  $HfO_2$  thin film annealed at  $800\,^{\circ}$ C in  $O_2$  was about  $5.5\times10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup>. After FGA, the interface trap density did not change.

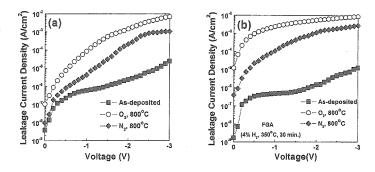

The leakage current characteristics of Pt/HfO<sub>2</sub>/SiO<sub>2</sub>/Si structure annealed in

$O_2$  and  $N_2$  ambient were shown in figure 5(a). The leakage current densities of the films annealed in  $O_2$  at 800 °C is about 8 × 10<sup>-5</sup> A/cm<sup>2</sup> at -1 V. However, the leakage current density of the samples heat treated in  $N_2$  at 800 °C is improved, which is about 3 × 10<sup>-6</sup> A/cm<sup>2</sup> at an applied voltage of -1 V. The higher leakage current densities of films annealed in  $O_2$  ambient than those in  $N_2$  were due to the increase of crystallinity of HfO<sub>2</sub> films, as shown in Fig. 1. After FAG, the leakage current density increased. Figure 5(b) shows the variation of leakage current densities of samples annealed in hydrogen ambient at 350 °C. The leakage current densities were abruptly increased by hydrogen forming gas anneal because oxygen loss in HfO<sub>2</sub> films during forming gas anneal increases oxygen vacancies and then increases charge carriers such as electron to achieve the charge neutrality.

FIGURE 5 Leakage current density of Pt/HfO<sub>2</sub>/SiO<sub>2</sub>/Si structure before FGA and after FGA. The capacitor area is  $3 \times 10^{-4}$  cm<sup>2</sup>.

### CONCLUSIONS

Hafnium oxide thin films for gate dielectric were deposited at  $300\,^{\circ}\text{C}$  on p-type Si(100) substrates by plasma enhanced chemical vapor deposition. The thickness of HfO<sub>2</sub> thin films decreases with increasing annealing temperature because of its high density. From the accumulation capacitance at 3 V, the CET of HfO<sub>2</sub> thin films annealed at  $800\,^{\circ}\text{C}$  in O<sub>2</sub> ambient are about  $29\,^{\circ}\text{A}$ .

Hysteresis of as-deposited gate dielectric was quite large but that of gate dielectric annealed at  $800\,^{\circ}\text{C}$  in  $O_2$  and  $N_2$  ambient was reduced to a negligible level without increase of the capacitance equivalent oxide thickness. The hysteresis in samples annealed at  $800\,^{\circ}\text{C}$  in  $O_2$  and  $N_2$  was reduced to a negligible level of about 20 mV. The leakage current densities of HfO<sub>2</sub> gate dielectric annealed at  $800\,^{\circ}\text{C}$  in  $O_2$  and  $N_2$  ambient were about  $8\times10^{-5}$  and  $3\times10^{-6}$  A/cm<sup>2</sup> at -1 V, respectively. After FAG, the electrical properties were not largely improved.

#### ACKNOWEDGMENTS

This work was performed under the support of Institute of Information Technology Assessment (IITA).

#### REFERENCES

- [1.] The International Technology Roadmap for Semiconductors (Semiconductor Industry Association, San Jose, CA, 1999).

- [2.] S. H. Lo, D. A. Buchanan, Y. Taur, and W. Wang, *IEEE Electron Device Lett.* 18, 209 (1997).

- [3.] B. H. Lee, L. Kang, R. Nieh, W. Qi, and J. C. Lee, *Appl. Phys. Lett.* 76, 1926 (2000).

- [4.] S. J. Lee, H. F. Luan, W. P. Bai, C. H. Lee, T. S. Jeon, Y. Senzaki, D. Roberts, and D. L. Kwong, *IEDM Tech. Dig.* 31 (2000).

- [5.] L. Kang, K. onishi, Y. Jeon, B. H. Lee, C. Kang, W. Qi, R. Nieh, S. Gopalan, R. Choi, and J. C. Lee, *IEDM Tech. Dig.* 35 (2000).

- [6.] B. H. Lee, R. Choi, L. Kang, S. Gopalan, R. Nieh, K. Onishi, Y Jeon, W. Qi, C. Kang, and J. C. Lee, *IEDM Tech. Dig.* 39 (2000).

- [7.] C. H. Lee, H. F. Luan, W. P. Bai, T. S. Jeon, Y. Senzaki, D. Roberts, and D. L. Kwong, *IEDM Tech. Dig.* 27 (2000).

- [8.] W. Qi, R. Nieh, B. H. Lee, L. Kang, Y. Jeon, and J. C. Lee, Appl. Phys. Lett. 77, 3269 (2000).

- [9.] Y. H. Wu, M. Y, Yang, A. Chin, W. J. Chen, and C. M. Kwei, *IEEE Electron Device Lett.* 21, 341 (2000).

- [10.] G. D. Wilk and R. M. Wallace, Appl. Phys. Lett. 74, 2854 (1999).

- [11.] G. D. Wilk and R. M. Wallace, Appl. Phys. Lett. 76, 112 (2000).

- [12.] M. Copel, E. Cartier, and F. M. Ross, Appl. Phys. Lett. 78, 1607 (2001).

- [13.] S. P. Muraka and C. C. Chang, Appl. Phys. Lett. 37, 639 (1980).

- [14.] M. Balog, M, Schieber, M. Michman, and S. Patai, *Thin Solid Films*, **41**, 247 (1977).

- [15.] L. M. Terman, Solid-State Electron, 5, 285 (1962)