# Amorphous Si/ Multicrystalline Si Heterojunctions for Photovoltaic Device Applications

Mahdi Farrokh Baroughi, Siva Sivoththaman

*Department of E&CE, University of Waterloo, Waterloo, Ontario, N2L3G1, Canada*

**Abstract.** Amorphous silicon/ multicrystalline silicon heterojunction diodes and photovoltaic cells are fabricated and characterized. Dark and illuminated current-voltage-temperature characteristics, high frequency capacitance-voltage and spectral response characteristics of the fabricated structures are employed for analysis of the a-Si/mc-Si heterojunctions. Interface quality is accessed by dark current-voltage-temperature characteristics and high frequency capacitance voltage measurement. Spectral response measurement on and off grain boundary is exploited to measure grain boundary degradation in heterojunction solar cells.

## INTRODUCTION

mc-Si based solar cells supply more than 30% of world's solar cell market. Current technologies employ high temperature diffusion processes for realizing solar cells<sup>1,2</sup>. In most of those materials however, the presence of large number of grains, grain boundaries, and crystallographic defects necessitates defect passivation, normally hydrogenation passivation. However, this imposes a temperature (T) limit for any post-passivation processes such as pn junction diffusion at high-T. Implementation of amorphous Si (a-Si)/crystalline Si heterojunctions (HJ) in place of diffused HJs in defective Si can keep the process temperature low thereby preserving the defect passivation. Unlike a-Si/single c-Si HJs<sup>3,4,5,6,7</sup>, little work have been reported on a-Si/mc-Si HJ solar cells<sup>8</sup>. This work presents low temperature realization and characterization of a-Si/mc-Si HJ solar cells. Dark and illuminated current-voltage-temperature (IVT), high frequency capacitance-voltage (CV), and External Quantum Efficiency (EQE) characteristics provide a unique work frame for qualifying HJs for photovoltaic applications.

## EXPERIMENTAL

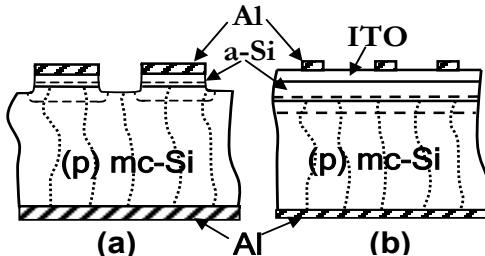

Devices with two different structures are fabricated for electrical and photovoltaic characterization of HJs. Figure 1(a) shows a HJ diode utilizing a p-type mc-Si wafer, an ultra thin intrinsic a-Si, and a thin ( $n^+$ ) a-Si

with aluminum layers as back and front contacts. Figure 1(b) shows a PV cell structure with addition of a transparent conductive oxide (TCO) layer providing a low resistive path for carriers. Detailed fabrication information is brought elsewhere<sup>9</sup>.

## RESULTS AND DISCUSSION

### 1. IVT Characterization

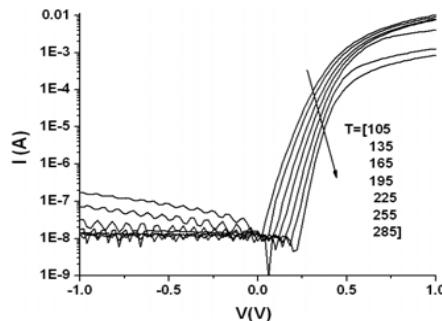

Dark IVT characteristic of a-Si/c-Si HJ reveals valuable information about carrier transport mechanisms in HJs. Like a-Si/c-Si HJ<sup>9,10,11</sup>, drift-diffusion, recombination at the heterointerface and Multi Tunneling Capture Emission (MTCE) are the most important carrier transport mechanisms in a-Si/mc-Si HJs. Temperature dependence of the diode saturation current and ideality factor are employed to investigate dominant carrier transport regimes in different bias conditions. IVT characteristics of a 4mm<sup>2</sup> a-Si / mc-Si HJ diode are shown in figure 2. Measurement results reveal bias dependence of dominant transport mechanism: current is recombination-dominated at low forward bias ( $V_A < 0.25$  V at 27°C), and drift-diffusion dominated at high bias regime (0.25V-0.5V). Relatively large ideality factor ( $\eta=1.35$ ) implies that passivation of mc-Si surface at heterointerface is incomplete and there is noticeable carrier recombination at interface.

Dark IVT of HJ diodes, with different sizes, on and off grain boundary doesn't show any noticeable change

because of grain boundary degradation. This is due to the fact that area current of the diode is much larger than grain boundary leakage current.

**Figure 1:** The structure of fabricated devices, (a) mesa etched heterojunction diode, (b) Heterojunction solar cell

**Figure 2:** Dark IVT curves of the HJ diode

## 2. High Frequency CV

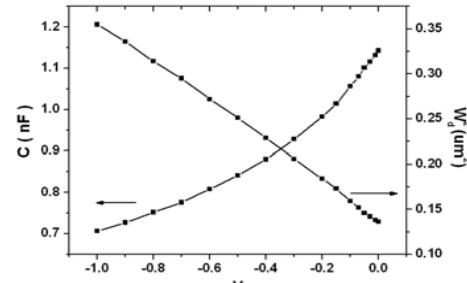

High Frequency CV (HFCV) characteristic is employed to qualify heterointerface quality by extracting HJ diode built in potential<sup>9</sup>. Figure 3 show the HFCV characteristic of the HJ diode with 2mm x 2mm area. This characterization results in 0.23V built in potential that is much lower than what is normally expected for a (n<sup>+</sup>) a-Si / (p) c-Si HJ diode (typical value: 0.65V). Low built in potential is another indication of low quality interface between a-Si and (p) mc-Si HJ. The interface quality is normally improved by inserting an optimized ultra thin intrinsic a-Si layer between (p) mc-Si and (n<sup>+</sup>) a-Si. Like IVT measurement, HFCV characteristic of HJ diodes on and off grain boundary doesn't show any noticeable change due to grain boundary degradation.

## 3. Illuminated IV and spectral response

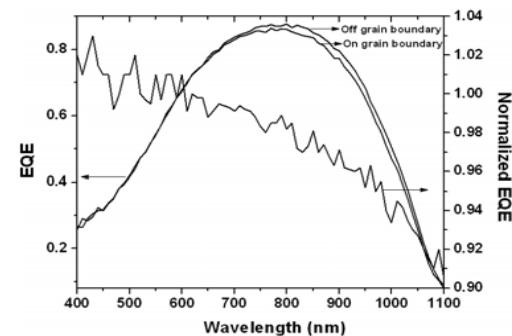

Illuminated IV of the HJ solar cells showed open circuit voltages of 550mV. Spectral response was measured using a micrometer-scale slit at various parts on the device, on- and off- grain boundaries. Carriers that are photo-generated far away from junction (by large  $\lambda$  photons) are more likely to recombine in the neighborhood of grain-boundaries since they need to diffuse longer distances towards the junction. A well-

passivated grain boundary should reduce this effect. Figure 4 shows EQE of device on and off grain boundary. The ratio of off grain boundary/on grain boundary EQE is shown in figure 4 as normalized EQE.

**Figure 3:** HFCV Characteristics of 4mm<sup>2</sup> HJ structure ( $W_d$ : depletion layer width)

**Figure 4:** EQE on- and off- grain boundary and normalized EQE

## CONCLUSION

a-Si/mc-Si HJ diode and solar cell structures have been fabricated and characterized. Interface quality and transport mechanisms are studied by IVT measurements. A low built-in potential of 0.23V, obtained by HFCV, indicates a defective heterointerface pointing to the need for a better interfacial passivation. Spectral response measurements show a lower response in the neighborhood of grain boundaries.

## REFERENCES

1. J. Nijs et al., *ITED*, **46**, 10 (1999)

2. M. A. Green, *Prog. in PV: Res. & App.*, **8**, 127 (2000)

3. M. Kolter et al., *Proc. 13<sup>th</sup> Euro. PVSEC*, 1995; 1526-1529

4. B. Jagannathan et al., *Sol. Egy. Mat. & solar cells*, **46**, 289 (1997)

5. R. Hussein et al., *Tech. Dig. 11<sup>th</sup> Int. PVSEC* 1999; 351

6. D. Rosa et al., *Proc. of 2<sup>nd</sup> WCPEC*, 1998; 1583-1586

7. N. Jensen et al., *Prog. in PV: Res. & App.*, **10**, 1 (2002)

8. D. Rosa et al., *Proc. of 2<sup>nd</sup> WCPEC*, 1998; 2440-2443

9. M. F. Baroughi et al., *JVST*, **22**, 1015 (2004)