# Low Cost and Highly Manufacturability 10Gb/s Mini-Flat Transmitter for Ethernet Applications

Shin-Ge Lee, Chih-Li Chen, Chu-Li Chao, Chun-Hsing Lee, Chen-Kun Chen, Li-Chun Liao, Chih-Hao Hsu, Fu-Yi Cheng, Cheng-Hung Tsai, Min-Fa Huang, Chiung-Hung Wang and Mu-Tao Chu

Opto-Electronics & System Laboratories, Industrial Technology Research Institute R936, Bld. 51, 195-8, Sec. 4, Chung-Hsing Rd. Chutung, Hsinchu 310, Taiwan, R.O.C. Tel:+886-3-5918443 E-mail: jasonlee@itri.org.twr

## ABSTRACT

The key issues of local-area-network (LAN) and storage-area-network (SAN) applications are to improve cost, manufacturability and reliability of optoelectronic devices in high speed transmission. The authors have demonstrated highly manufacturability, reliability and thermal stability mini-transmitter for 10Gb/s Ethernet applications in this paper. Passive alignment technology is a way to improve manufacturability of optoelectronic devices in the future. However, the assembly yield rate of conventional LD chip on silicon optical bench to fiber is guite limited due to restricted optical alignment tolerance (< 1um). In this study, a novel two lens structure of 10Gb/s LC receptacle type optical miniflat transmitter is designed and demonstrated to exhibit above 20% coupling efficiency with less than ±6um aligned deviation. Moreover, a high resistivity silicon optical bench ( $1k\Omega/cm$ ) and pressure-free bonding technique using the electroplated AuSn solder are also adopted to guarantee the transmitted performance in high frequency operation. The eye diagram of 10Gb/s mini-flat transmitter developed in this study showing the excellent quality obtained passing 10Gb/s Ethernet mask test with 20% margin. And the extinction ratio of transmitter is also proved to above 6dB at room temperature. The response of monitor PD is also examined up to 80% by mirror coating on silicon V-groove. Thermal stability of 10Gb/s mini-flat transmitter is another critical issue in high speed transmission. The performance of temperature stabilized transmitter over wide case temperature range is also evaluated in this study. The optical eye diagram of 10Gb/s transmitter developed in this paper showing excellent eye quality passing 10Gb/s Ethernet mask test between 0°C to 80°C. Finally, the reliability of transmitter is also performed. The reliability data indicate that the optical alignment of these modules are stable and observed essentially low variations in optical coupling as results of 1000 hours damp heat and 1000 temperature cycling durations.

## **1. INTRODUCTION**

The recent increase in the amount of data traffic requires optical communication systems operating at 10Gb/s and above even in LAN and MAN such as 10Gigabit Ethernet (10GE) and 10Gigabit Fiber-Channel (10GFC). One of the most key issue is reducing the cost, size and power consumption of optical components in these applications. There have been many studies on improving the performance of 10Gb/s 1310nm DFB chip with box type packages, especially the high frequency performance at high temperature [1-2]. Passive aligned technique is a way to improve manufacturability of optoelectronic devices in high speed transmission [3-5]. However, it can be achieved without high accuracy flip chip bonder  $\cdot$  perfect process of SiOB, and accuracy packaging flow to keep the total alignment tolerance below  $\pm 1\mu$ m. In this paper, the authors demonstrated a novel two lenses semi-passive alignment structure not only to loose the tolerance but also improve the coupling efficiency up to 35% with general semiconductor process and optoelectronic packaging equipments. Moreover, the 10Gb/s 1310nm uncooled direct modulation mini-flat transmitter developed in this paper is also proven to follow the requirements of 10Gb/s Ethernet transceiver modules. The remaining of this paper is organized as follows: section 2 will describe the electrical design and analysis of SiOB and following packaging and evaluations are points in sequential sections, respectively. Finally, the conclusions of this study are given in last section.

Semiconductor and Organic Optoelectronic Materials and Devices, edited by Chung-En Zah, Yi Luo, Shinji Tsuji, Proceedings of SPIE Vol. 5624 (SPIE, Bellingham, WA, 2005) · 0277-786X/05/\$15 · doi: 10.1117/12.575901

## 2. ELECTRICAL DESIGN AND ANALYSIS

The core factors of designing the SiOB in 10Gb/s operations are including the electrical characteristics of material and the parameters of process. The electrical parameters of silicon, such like the dielectric constant, loss-tangent and dielectric conductivity will mainly determine the transmission performance of signal. On the other hand, the skin effect, thickness and effective conductivity of compound metal will also deeply influence the transmission loss of signal. Therefore, all the electrical parameters mentioned will be calculated by the simulation tool to predict and specify the requirement and the probable tolerance of process before the actual implementation of SiOB.

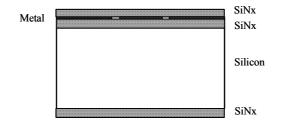

Fig. 1 depicts the simulation model of SiOB, and the simulation conditions are listed in Table 1. Table 1 lists the electrical characteristics of dielectric layers and metal layers. The thickness of the silicon, SiNx, and metal will also affect the impedance design. The surface resistance and skin effect of the metal layer is an effective value that represents synthetic conductivity of three different metals. As operating at high frequency, it is supposed that the most signal is transmitted along the Au-layer.

Fig. 1 Simulation model of SiOB

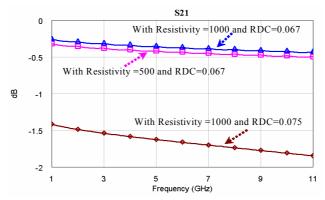

The propagation loss between different resistivity of silicon wafer is also analyzed in this study. Fig. 2 shows that  $500\Omega/cm$  resistivity silicon wafer causes the transmission loss more serious than silicon wafer with  $1k\Omega/cm$  resistivity. However, if effective surface resistance  $R_{DC}$  of the compound metal is changed from 0.067 to 0.075, that means more signal transmit in the Ti/Pi-layer in the low frequency range, the transmission loss will become more significant. From the simulation results, the dimension of the RF transmission line is determined. Besides, the reasonable thickness of silicon, SiNx and metal are specified for following SiOB processing.

| Material | Electrical Parameters                 |                                            |                                          |           |

|----------|---------------------------------------|--------------------------------------------|------------------------------------------|-----------|

| Silicon  | Dielectric<br>Constant                | Loss Tangent                               | Resistivity                              | Thickness |

|          | 12                                    | 0.0004                                     | 1kΩ/cm                                   | 660 µm    |

| Metal    | Surface<br>Resistance R <sub>DC</sub> | Skin Effect<br>Coefficient R <sub>RF</sub> | Thickness of Ti / Pt / Au                |           |

|          | 0.067Ω/sq                             | 9.81e-7                                    | 500Å/500Å/3500Å                          |           |

| SiNx     | Dielectric<br>Constant                | Loss Tangent                               | Thickness                                |           |

|          | 7                                     | 0.00001                                    | Above metal: 3000Å<br>Below metal: 5000Å |           |

Table 1 Simulation conditions of SiOB.

Fig. 2 The simulation results with different resistivity of silicon wafer

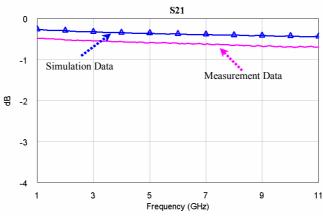

The comparison of measurement data and simulation results are displayed in Fig. 3. The line with mark represents the simulation data and the measurement data is described in solid line without mark. The results of S21 depicts that the exactly transmission loss is around  $0.5\sim0.6$ dB. The difference between simulation and measurement results is about 0.3dB.

Fig. 3 The comparison between measurement data and simulation result of SiOB

## **3. OPTICAL DESIGN AND ANALYSIS**

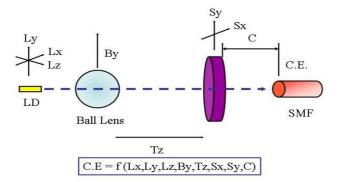

The high coupling efficiency(>20%)  $\cdot$  receptacle type  $\cdot$  low cost optical transmitter are some key issues to meet the requirements for 10Gb/s Ethernet applications. However, the traditional butt coupling optical system used in SiOB requires a high accuracy flip chip bonder  $\cdot$  perfect process of SiOB, and accuracy packaging flow to keep the total alignment tolerance below ±1µm, the tolerance is too tight for mass production. Therefore, the semi-passive double-lenses optical system including a ball lens and an aspheric lens is designed not only to loose the system tolerance but to improve the coupling efficiency of 10Gb/s mini-flat transmitter. Figure 4 shows the schematic structure of double-lenses optical system, where C.E. is the coupling efficiency, Lx, Ly, Lz are LD axis shifted in x  $\cdot$  y  $\cdot$  z directions, respectively, By is the radius 800um BK7 ball lens axis shifted in y direction, Sx, Sy, Tz represent the axis shift of the aspherical lens in x, y, z direction relative to the ball lens, and C is the distance between single-mode fiber (SMF) and aspheric lens.

Fig. 4 Schematic structure of 10Gb/s mini-flat transmitter optical system

According to the schematic structure of 10Gb/s mini-flat transmitter optical system shown in Fig. 4, the coupling efficiency of system can be described as the assembly function as Eq. (1)

$$C.E. = f(Lx, Ly, Lz, By, Sx, Sy, Tz, C)$$

(1)

And the coupling efficiency can simplify as Eq. (2) due to cylinder symmetrical of SiOB.

C.

$$E_{\rm e} = f(\tilde{R}_{\rm p}, Lz, Sx, Sy, Tz, C)$$

<sup>(2)</sup>

where  $\vec{R}_{B} = \sqrt{(\vec{L}x)^{2} + (\vec{L}y + \vec{B}y)^{2}}$ .

Let the axis shifted of aspheric lens as  $\vec{R}_{L} = \sqrt{Sx^2 + Sy^2}$ , where (Sx, Sy) are the shift of aspheric lens on x, y axis. Then the coupling efficiency can be further defined as Eq. (3)

$$C.E. = f(\vec{R}_{B}, \vec{R}_{I}, Lz, Tz, C)$$

(3)

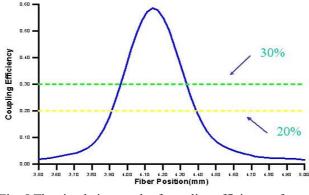

Two cases are studied in this paper, one is the case with high accuracy flip chip bonder  $\cdot$  perfect process of SiOB, and accuracy packaging flow. And the following are the assembling conditions of case 1:  $\vec{R}_B = 5\mu m$ ,  $\vec{R}_L = 10\mu m$ , Lz = 1 $\mu m$  and Tz = 100 $\mu m$ . Fig. 5 shows the simulation results of case 1. The coupling efficiency of case 1 is calculated above 58.8%. Beside, the coupling efficiency of case 1 is also simulated to remain 50% with  $\pm 2\mu m$  deviation in final welding process.

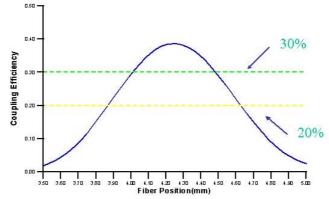

The other is the case with  $\pm 5\mu$ m flip chip bonder  $\cdot$  general process of SiOB, and packaging flow. And the following are the assembling conditions the authors suggested according to above situations in case 2:  $\vec{R}_B = 20\mu m$ ,  $\vec{R}_L = 150\mu m$ , Lz =15 $\mu$ m and Tz = 1000 $\mu$ m. Fig. 6 shows the simulation results of case 2. The coupling efficiency of case 2 is simulated about 37.9%. Beside, the coupling efficiency of case 2 is also simulated to keep 36.1% with  $\pm 2\mu$ m deviation in final welding process.

Fig. 5 The simulation result of coupling efficiency of case 1

262 Proc. of SPIE Vol. 5624

Fig. 6 The simulation result of coupling efficiency of case 2

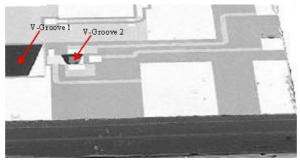

## 4. SILICON OPTICAL BENCH FABRICATION

It's widely used for bulk micromachining of single crystal to fabricate the packaging platform for optical devices. The structure nature of silicon makes it possible to fabricate the precise three-dimensional shape. In general, silicon has high etching selectivity of (100) to (110) plane in anisotropic wet etching, and it offers a fascinate advantage to apply silicon on optoelectronic device packaging. In this paper we present a low-cost fabrication process of SiOB which contains two Silicon V-grooves, electrical circuit and eutectic gold-tin solder pad. A 964µm wide V-groove is created for holding the 800µm BK7 ball lens in place and the smaller one is coated with gold on the sidewalk acted as a mirror reflecting light to monitor photo diode. The main processing steps are described as following:

Step A. Start from a single polished p-type silicon wafer with orientation of (100). The wafer thickness is 680 um.

Step B. The first of making a SiOB is depositing a 5000Å thick silicon nitride (SiNx) layer on  $1k\Omega/cm$  resistivity silicon wafer by LPCVD(low pressure chemical vapor deposition). For protection from 45% KOH etchant, both sides of deposited silicon nitride layers are necessary.

Step C. Lithography and RIE (reactive ion etching) process are accomplished to remove the SiNx layer on V-groove area.

Step D. The silicon wafer is immersed into KOH solution. By controlling the etching time precisely and maintaining the temperature as  $60^{\circ}$ C, the width and depth of V-groove are  $964\pm2\mu$ m and  $400\mu$ m made to allow the passive alignment of ball lens, respectively.

*Step E.* E-beam evaporate the conductive layer (Ti/Pt/Au, 500Å/500Å/3500Å) on the silicon wafer after the V-grooves etchant have been created. With lithography process and commercial etchant, the conductive layer is selectively removed again and electrical circuit created.

Step F. To avoid short circuit on SiOB, the second SiNx layer (3000Å) is deposited on the surface of gold layer by PECVD.

Step G. Lithography and RIE (reactive ion etching) process are accomplished to remove the SiNx layer on plating area.

Step H. Thermal coating 3µm gold-tin to form solder plates, thick photoresist lithography to pattern gold-tin.

Fig. 7 represents the photography of the fabricated SiOB for 10Gb/s mini-flat transmitter. The width tolerances of both V-grooves etchant on SiOB are demonstrated in  $\pm 2\mu m$ .

Fig. 7 The photography of fabricated SiOB.

## **5. PACKAGING**

The fabricated SiOB provide a support and alignment platform for the LD chip, monitor PD chip, ball lens and other electrical passive devices (resistor, capacitor, thermistor, etc.). The LD chips are accurately bonded junction down on the SiOB according to the alignment features on LD and SiOB with a flip-chip bonder of  $\pm 5\mu$ m accuracy. The ball lens is passive-aligned on the V-groove and fixed with epoxy adhesive. After all the devices are assembled on the SiOB, the SiOB is wire bonded for electrically connection. The SiOB is then performed inside and bonded along with the 10Gb/s mini-flat package with the same system of the flip-chip bonder. One issue must be considered when the bench is aligned to the package, the LD chip is not exactly in the center of the bench due to the deviation of die sawing error of the SiOB. Therefore, the center of LD chip on SiOB (> 20µm) must be compensated as could as possible by measuring and shifting the center misalignment of bench and LD chip. After SiOB is fixed, an isolator is also bonded in similar process. The isolator is used for reducing optical feedback which causes the optical instability and increases relative intensity noise (RIN). A seam sealer is used to guarantee the hermetic of 10Gb/s mini-flat transmitter. A lid is attached to the Mini-Flat package by parallel seam welding with 1.5KW welding power. A leakage test is performed after sealing to evaluate the hermetic of the package, the leakage is below 1 x 10<sup>-11</sup> Pam<sup>3</sup>/s .

After the package is sealed, then the second aspherical lens and fiber ferrule are expected to attached to the sealed package for optical connection. The second aspherical lens is used for focusing the collimated light emitting from the window of the package, the  $2^{nd}$  lens is attached to the package via a lens holder, and the fiber ferrule is attached to the lens holder via a sleeve, all the fixation are done by laser welding method on a commercial laser welder system. The following are the welding parameters of lens holder  $\cdot$  sleeve and fiber ferrule, respectively. The laser welding parameters are 1.5KW-5ms for lens holder and package, 1.8kW-5ms for sleeve and ferrule and 1.2kW-3ms for sleeve and lens holder. The maximum coupling efficiency is attained 35%, and the post laser welding shift loss is below 0.5dB. Fig. 8 shows the photography of LC receptacle type and pigtail type 10Gb/s mini-flat transmitter developed in this study. The dimension of the transmitter is 13.2 x 7.4 x 4.34mm, which is about 1/3 the volume of a traditional butterfly module.

Fig. 8 The photography of LC receptacle type and pigtail type 10Gb/s mini-flat transmitter

## 6. PERFORMANCE AND RELIABILITY

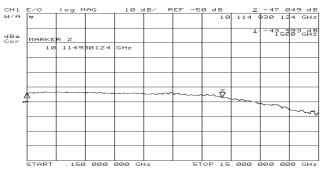

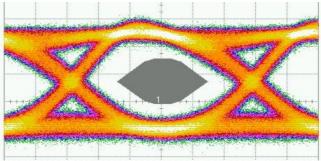

Fig. 9 shows the measured frequency response of 10Gb/s mini-flat transmitter operated at 50mA biased current and permitted a modulated bandwidth over 10GHz at room temperature. The back to back eye diagram of 10Gb/s direct

264 Proc. of SPIE Vol. 5624

modulation transmitter operated with 10.3125Gb/s Pseudo-Random-Binary-Sequence (PRBS)  $2^{31}$ -1 pattern is also evaluated in Fig. 10. And exhibits an open and clear eye diagram complete accomplished the eye template of 10GE with 30% margin. The response of monitor PD is also examined up to 80% by mirror coating on silicon V-groove. The 10Gb/s 1310nm mini-flat transmitter developed in this paper has demonstrated excellent performance for future high speed applications.

Fig. 9 Frequency response of 10Gb/s 1310nm mini-flat transmitter

Fig. 10 Eye diagram of 10Gb/s 1310nm mini-flat transmitter with 30% mask margin at room temperature

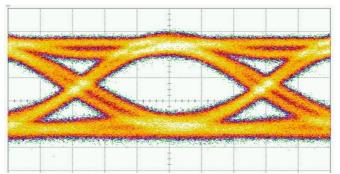

The performance of the temperature stabilized transmitter over wide case temperature is also experimented. Thermalelectrical cooler (TEC) is a usual cooling element, but expensive one in box type transmitter for long haul or DWDM transport systems. However, it is quite difficult to combine a cooling element in a transmitter and to meet the low cost, compact size and low power consumption requirements of 10GE transceiver modules. The characteristic temperature of a laser diode determines the thermal stability. The high band-gap offset InGaAlAs laser diode is adopted to approach the uncooled aim with its high characteristic temperature. The 10Gb/s 1310nm InGaAlAs mini-flat transmitter is measured at  $80^{\circ}$ C case temperature to verify thermal stability in high temperature. The eye diagram of 10Gb/s transmitter operated at  $80^{\circ}$ C case temperature with 10.3125Gb/s PRBS 2<sup>31</sup>-1 pattern is tested and accomplished the eye mask as shown in Fig. 11.

Fig. 11 Eye diagram of 10Gb/s 1310nm mini-flat transmitter at 80°C

Finally, the reliability issues of 10Gb/s mini-flat transmitter are also considered and performed according to Telcordia-GR468-CORE in this paper. In the bench level, die shear test of LD chip and wire bond strength test are performed, respectively. The die shear test is evaluated over 100gm, and the wire bond strength is over 4gm, and all meet the requirements of MIL-STD-883 standard. The mechanical integrity issues including mechanical shock, vibration and fiber pull are performed, and also demonstrated qualified. The endurance test of damp heat and temperature cycling are chosen to test. The test condition of damp heat test is  $85\%/85^{\circ}$ C, 1000hrs, and the condition of temperature cycling test is -40°C to  $85^{\circ}$ C, 1000 cycles. The launch power variation of 10Gb/s mini-flat transmitter is evaluated during the tests, and the launch power deviation is both below  $\pm 0.5$ dB after the damp heat and temperature cycling test.

## 7. CONCLUSIONS

Passive alignment technique is a way to promote manufacturability of optoelectronic devices in the future. However, the assembly yield rate of conventional LD chip on SiOB to fiber is quite limited due to restricted optical alignment tolerance. In this study, the novel two lenses semi-passive structure of 10Gb/s LC receptacle type and pigtail type optical 1310nm mini-flat transmitter is designed and demonstrated to exhibit about 35% coupling efficiency with  $\pm 5\mu$ m accuracy flip chip bonder  $\cdot$  general process of SiOB and packaging flow. Moreover, a high resistivity SiOB and pressure-free bonding technique using the electroplated AuSn solder are also adopted to guarantee the transmitted performance in high speed operation. The eye diagram of 10Gb/s mini-flat transmitter developed in this study showed the excellent quality obtained passing 10GE mask test with 30% margin. And the extinction ratio of transmitter is also proved to above 6dB at room temperature.

The performance of temperature stabilized transmitter over wide case temperature range is also experimented and pass 10Gb/s Ethernet mask test at  $80^{\circ}$ C. Finally, the reliability tests of 10Gb/s mini-flat transmitter are performed. The reliability data indicate that the optical alignment of these modules are stable and observed essentially low variations in optical coupling as a result of 1000 hours and 1000 cycles damp heat and temperature cycling durations, respectively.

#### REFERENCES

- 1. A. Benzoni, M. Downie, B. Kasper, J. Paslaski, E. Peral, X.-M Wu., T. Schrans, C. Tsai, and I. Ury, "High speed, high performance laser module", *Proc* 50<sup>th</sup> *Electronic Components and Technology Conference*, 2000, pp. 465-468.

- 2. M. Okayasu, "10Gbit/s 1.3µm DFB-LD module in 0.5cc ceramic package for LAN/MAN applications", *Electron Lett.*, **37** (2001), pp. 303-304.

- 3. S. Hwang, J. Ku, J. Won, E. Yoon, I. Song, D. Chang, D. Bang, J. Kang, M. Um, S. Park, S. Lee, D. Jang, M. Park, "10Gbps uncooled DFB LD module by the optimal EOTM design", *European Conference on Optical Communication 2002*, 2002.

- M. H. Choi, H. J. Koh, E. S. Yoon, K. C. Shin, K. C. Song, "Self-aligning silicon groove technology platform for the low cost optical module", *Proc 49<sup>th</sup> Electronic Components and Technology Conference 1999*, 1999, pp. 1140-1144.

266 Proc. of SPIE Vol. 5624

5. Y. Kishida, Y. Niwa, Y. Kuba, R. Komeda, K. Setoguchi, T. Matsubara, M. Yanagisawa, S. Tanahashi, "Surface mountable package (OptoBGA<sup>TM</sup>) for 10G data link", *Proc* 51<sup>th</sup> Electronic Components and Technology Conference, 2001, pp. 1427-1430.