## GaSb Metal-Oxide-Semiconductor Capacitors with Atomic-Layer-Deposited HfAlO as Gate Dielectric

Chen Wang,<sup>a,b</sup> Min Xu,<sup>b</sup> Jiangjiang Gu,<sup>b</sup> David Wei Zhang,<sup>a</sup> and Peide D. Ye<sup>b,\*z</sup>

<sup>a</sup>State Key Laboratory of ASIC and System, School of Microelectronics, Fudan University, Shanghai 200433, China

<sup>b</sup>School of Electrical and Computer Engineering and Birck Nanotechnology Center, Purdue University, West Lafayette, Indiana 47907, USA

An interface characterization of p-type GaSb metal-oxide-semiconductor (MOS) structures has been performed with Al-first and Hf-first HfAlO gate dielectrics deposited via atomic layer deposition. The Al-first process is found to improve the characteristic of high- $k$ /GaSb MOS such as breakdown strength, frequency dispersion in accumulation region and gate dependent capacitance modulation. From temperature dependent conductance method, an interface trap density of  $4 \times 10^{12} \text{ cm}^{-2} \text{ eV}^{-1}$  near the valence band edge is extracted for Al-first HfAlO/GaSb. The border trap density is found to be  $4.5 \times 10^{19} \text{ cm}^{-3}$  with a barrier height of 2.75 eV below the valence band edge of GaSb.

© 2011 The Electrochemical Society. [DOI: 10.1149/2.001203esl] All rights reserved.

Manuscript submitted October 17, 2011; revised manuscript received November 15, 2011. Published December 28, 2011.

III-V materials have recently been extensively studied as potential candidates for post-Si complementary metal-oxide-semiconductor (CMOS) channel materials. The main obstacle to implement III-V compound semiconductors for CMOS applications is the lack of high-quality, thermodynamically stable insulators with low interface trap densities. Recently, significant progress has been achieved on the improvement of high- $k$ /III-V interfaces with atomic-layer-deposited (ALD)  $\text{Al}_2\text{O}_3$ ,<sup>1</sup> HfAlO<sup>2,3</sup> and  $\text{HfO}_2$ <sup>4-6</sup> dielectrics. Most III-V semiconductors have very high electron mobility and saturation velocity, making them ideal for n-channel materials. These properties have allowed high drive current and high transconductance to be realized on high- $k$ /III-V n-channel metal-oxide-semiconductor field-effect transistors (MOSFETs) at deep-submicron gate lengths.<sup>7-9</sup> On the other hand, the hole mobilities of many III-Vs are relatively low and limited progress has been made on III-V p-channel MOSFETs.<sup>10-13</sup> GaSb has a bandgap of 0.73 eV and is near lattice matched to the n-channel material InAs. The hole mobility of GaSb is around  $1000 \text{ cm}^2/\text{V} \cdot \text{s}$ , which is much higher than Si and most other III-V materials.<sup>14</sup> The effective density of states in the valence band ( $N_V$ ) of GaSb is as high as  $1.8 \times 10^{19} \text{ cm}^{-3}$ , which is also favorable for realizing high-performance GaSb PMOSFETs. Meanwhile, the charge neutral level lies near the valence band edge, similar to that of Ge. These unique properties make strong hole inversion easy to realize in GaSb and therefore it is suitable for III-V p-channel MOSFET applications.<sup>15-17</sup> Recently, high-performance GaSb p-channel MOSFETs with ALD  $\text{Al}_2\text{O}_3$  gate dielectric have been demonstrated.<sup>12,13</sup> To further decrease the equivalent oxide thickness (EOT), the integration of gate oxides such as HfAlO and  $\text{HfO}_2$  which possess higher dielectric constant on GaSb is necessary and detailed study of their interface quality is lacking.

In this letter, we systematically study the interface and dielectric properties of various high- $k$ /GaSb systems with ALD HfAlO as gate dielectric by using capacitance-voltage (CV) measurements. The Al-first ALD process is shown to have superior dielectric strength as well as interface quality as compared to the Hf-first counterpart. The low temperature conductance method and a distributed model of direct tunneling are applied to extract the interface trap and border trap density quantitatively. The 600°C post deposition annealing (PDA) is found to help suppress the border traps, but also deteriorate the interface quality of the HfAlO/GaSb capacitors.

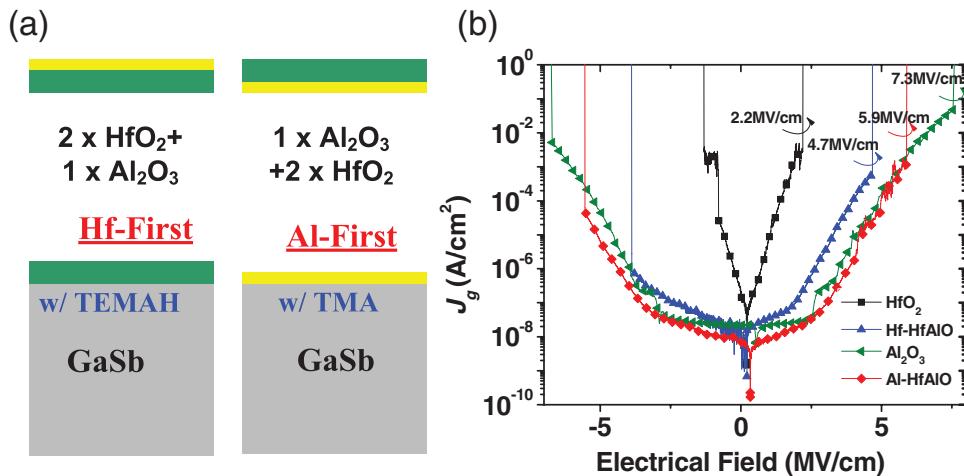

The fabrication of MOS capacitors starts with a p-type GaSb substrate having a doping concentration of  $4.6 \times 10^{16} \text{ cm}^{-3}$ . Two different ALD processes (Hf-first or Al-first) were developed to deposit HfAlO using an ASM F-120 ALD reactor. As illustrated in Figure 1,

after degreasing in acetone, methanol, and isopropanol, 8 nm Al-first or Hf-first HfAlO was deposited at 200°C. Previous experiments demonstrate that a low temperature ALD process at 200°C is favorable for passivating GaSb interface.<sup>11-13</sup> Each complete layer of Hf-first HfAlO was deposited by two cycles of  $\text{HfO}_2$  followed by one cycle of  $\text{Al}_2\text{O}_3$ . The compositional ratio of Hf:Al was about 2:1. With the same Hf:Al ratio, Al-first HfAlO was deposited by one cycle of  $\text{Al}_2\text{O}_3$  followed by two cycles of  $\text{HfO}_2$  in one complete layer of HfAlO. The  $\text{Al}_2\text{O}_3$  was deposited using trimethylaluminum (TMA) and water, while  $\text{HfO}_2$  was deposited using tetrakisethylmethylamino-hafnium (TEMAH) and water. Figure 1a shows a schematic diagram for the Al-first and Hf-first HfAlO deposition process. The PDA process was then performed at 600°C in  $\text{N}_2$  ambient for 30 s. The PDA condition is chosen since previous GaSb PMOSFET fabrication requires a 600°C implantation activation temperature.<sup>13</sup> Ni/Au was electron beam evaporated as the gate electrodes. Control samples with ALD 8 nm  $\text{Al}_2\text{O}_3$  and 20 nm  $\text{HfO}_2$  as gate dielectrics were also fabricated. The leakage current was measured using an HP4156A semiconductor parameter analyzer, and the capacitance was measured using an Agilent E4980A precision LCR meter with frequencies varying from 1 kHz to 1 MHz.

Figure 1b shows the gate leakage current density of p-type GaSb MOS capacitors with Hf-first HfAlO, Al-first HfAlO,  $\text{HfO}_2$  and  $\text{Al}_2\text{O}_3$  gate dielectrics after 600°C PDA. The HfAlO dielectric films exhibit lower leakage current and higher breakdown voltage than  $\text{HfO}_2$  films. The gate leakage current density at 3 V gate bias is about  $2.5 \times 10^{-8} \text{ A}/\text{cm}^2$  for Al-first HfAlO and  $5.8 \times 10^{-8} \text{ A}/\text{cm}^2$  for Hf-first HfAlO samples. Meanwhile, the hard breakdown electrical strength is 5.9 MV/cm for Al-first HfAlO samples, 4.7 MV/cm for Hf-first HfAlO and 7.3 MV/cm for  $\text{Al}_2\text{O}_3$  samples. ALD  $\text{HfO}_2$  film is previously shown to crystallize at 600°C annealing temperature.<sup>18,19</sup> The larger leakage current in  $\text{HfO}_2$  devices is therefore attributed to the creation of leakage paths at crystal grain boundaries formed after  $\text{HfO}_2$  phase change from amorphous to polycrystalline. On the other hand, ALD  $\text{Al}_2\text{O}_3$  film remains amorphous up to around 900°C.<sup>20</sup> The insertion of  $\text{Al}_2\text{O}_3$  cycles suppresses  $\text{HfO}_2$  crystallization and reduces the leakage paths in  $\text{HfO}_2$ .

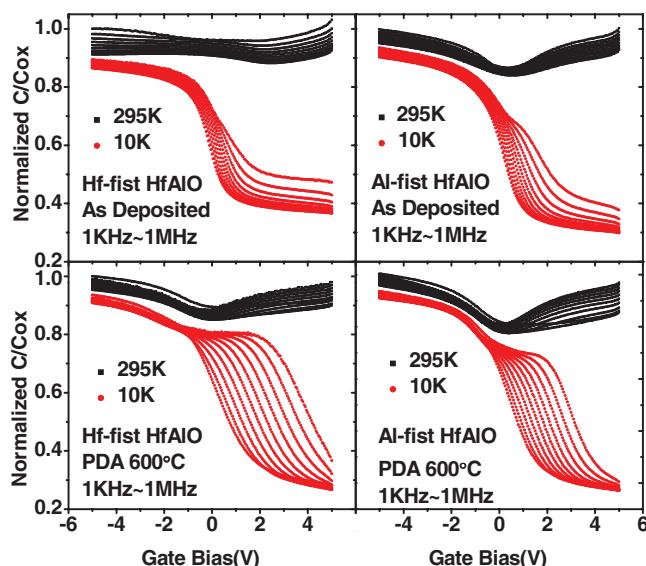

Figure 2 shows the multi-frequency C-V characteristics from 1 kHz to 1 MHz on Hf-first and Al-first HfAlO GaSb MOS capacitors before and after PDA at 295 K and 10 K. The gate voltage is swept from 5 V to -5 V. From the room temperature curves, Al-first HfAlO gated samples show significantly better C-V characteristics than the Hf-first samples. A sharper transition from accumulation to depletion is obtained on Al-first HfAlO films both with and without annealing, and the capacitance modulation by the gate is more than 50% greater on Al-first HfAlO than Hf-first one. Note that the Hf-first HfAlO samples do show partially pinned C-V features before PDA. This indicates that Al-first HfAlO is more effective in passivating interface traps in the

\* Electrochemical Society Active Member.

<sup>z</sup> E-mail: yep@purdue.edu

**Figure 1.** (a) Illustration of Hf-first and Al-first HfAlO ALD process (b) Gate leakage current density  $J_g$  (A/cm<sup>2</sup>) versus electric field (MV/cm) on HfO<sub>2</sub>, Hf-first HfAlO, Al<sub>2</sub>O<sub>3</sub> and Al-first HfAlO capacitors after PDA at 600°C. Here, the electrical field is defined by  $(V_g - V_{FB})/T_{ox}$ , where  $V_{FB}$  is flatband voltage and  $T_{ox}$  is physical oxide thickness.

GaSb bandgap. Moreover, Al-first HfAlO MOS capacitors show less frequency dispersion in the accumulation region than Hf-first HfAlO MOS capacitors. At a gate voltage of  $-3\text{V}$ , the frequency dispersion is about 3% per decade for Hf-first HfAlO films and 1% per decade for Al-first HfAlO films. This is ascribed to the suppression of border traps near the interface by the first Al<sub>2</sub>O<sub>3</sub> layer deposited in Al-first samples.<sup>21</sup> The smaller frequency dispersion, along with the stronger gate-dependent modulation, implies higher quality of dielectric and interface properties of Al-first ALD HfAlO on GaSb over the Hf-first counterpart.

The above observation is further verified by the low-temperature C-V measurements in red curves as shown in Figure 2. At 10 K, minority carriers (electrons) and part of the interface trap responses are suppressed. It is found that smaller frequency dispersion in the accumulation region is also achieved on Al-first samples. The accumulation capacitance and the frequency dispersion do not decrease significantly on Al-first HfAlO films at 10 K, indicating that true accumulation has been realized with good dielectric quality and reasonable interface quality near the valence band edge.<sup>22</sup> For the samples made with the

PDA process, larger bumps are observed in the depletion region at 10 K for both Hf-first and Al-first samples, implying more interface traps were induced by 600°C PDA near the midgap. This could be a result of Hf diffusion into the interface after PDA. In future work, extra ultrathin Al<sub>2</sub>O<sub>3</sub> layers can be inserted as the diffusion barriers to prevent the interface degradation from the Hf diffusion during PDA.<sup>13</sup> On the other hand, the frequency dispersion in accumulation region is improved with PDA treatment. This is attributed to the suppression of border traps in the oxides due to the annealing. Therefore, the PDA process on HfAlO/GaSb capacitors allows for a trade-off between dielectric quality and interface quality.

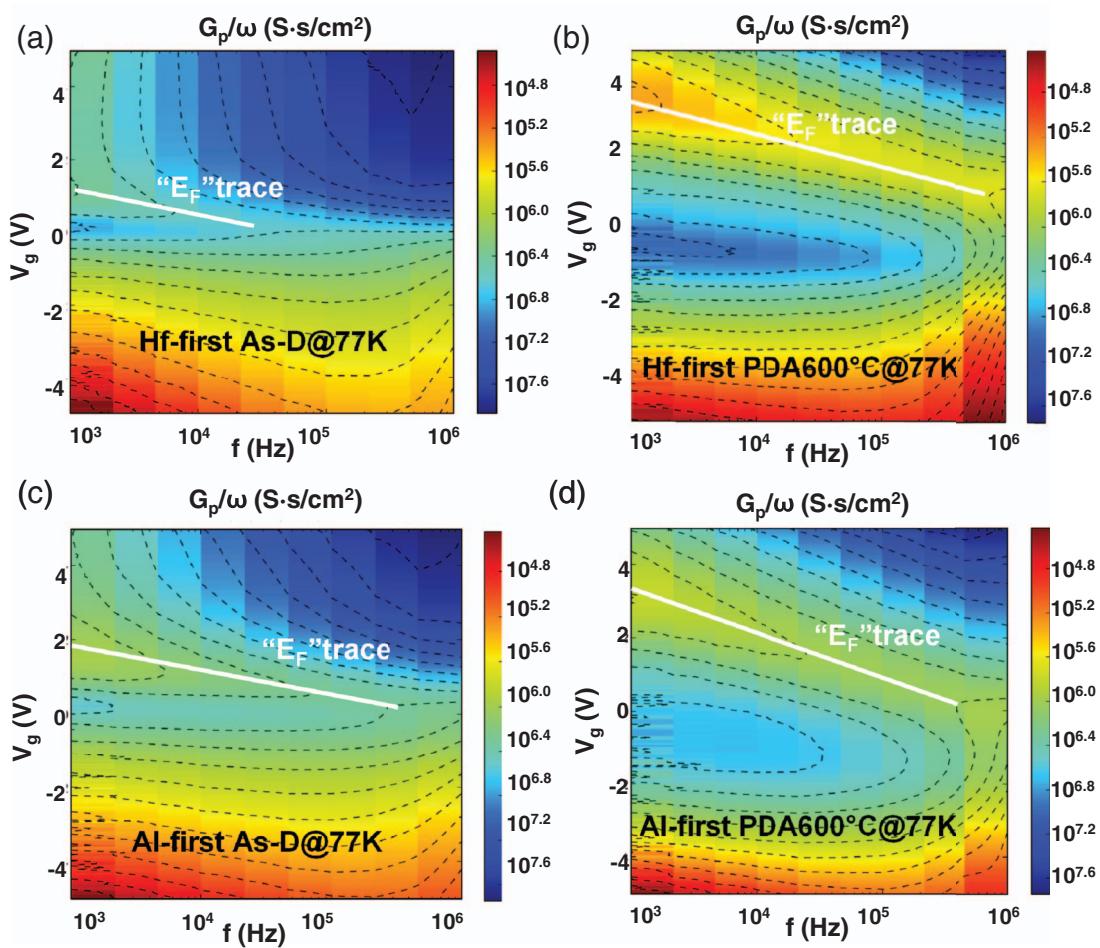

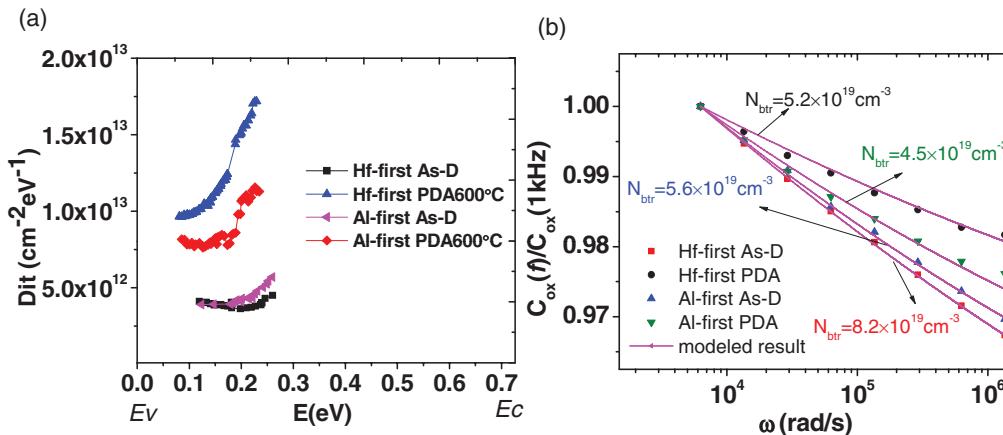

The temperature-dependent conductance method is applied to quantitatively map the  $D_{it}$  distribution from  $E_v$  to midgap.<sup>23</sup> Figure 3 shows the conductance maps for Hf-first and Al-first samples with and without PDA at 77 K. The Fermi level movement ( $E_F$  trace) is highlighted in each case and provides a qualitative evaluation of the gate modulation efficiency. It is found that the Al-first HfAlO without PDA process offers the most effective modulation and thus provides the best interface quality on GaSb. This is consistent with the C-V characteristics shown in Figure 2. Figure 4a shows the  $D_{it}$  distribution extracted from conductance method at 10 K. Al-first HfAlO shows the lowest  $D_{it}$  towards the valence band edge ( $\sim 4 \times 10^{12} \text{ cm}^{-2} \text{ eV}^{-1}$ ). The PDA process is found to increase the interface trap density in the bandgap, being consistent with the much larger bumps in CV characteristics at 10 K shown in Figure 2.

Since the frequency dispersion in the accumulation region of HfAlO films starts to be insensitive to temperature below 77 K (not shown here), a distributed model<sup>21</sup> related with direct tunneling was applied to extract the border trap density near the interface. Figure 4b summarizes all measured normalized capacitance for Hf-first and Al-first HfAlO samples with or without PDA versus frequency ( $\omega$ ) in dots and simulated results in lines. The capacitances are measured at  $V_g = -3.9 \text{ V}$  and  $T = 10 \text{ K}$  with frequency range of 1 kHz~1 MHz. Carrier effective mass in HfAlO is chosen to be  $0.18m_0$ .<sup>24</sup> The time constant associated with charge exchange between border traps and semiconductor is  $2.8 \times 10^{-10} \text{ s}$ . The semiconductor capacitance is obtained from the numerically simulated value of  $5.9 \mu\text{F/cm}^2$ . By fitting the border traps density  $N_{bt}$ , good agreements are achieved between model and the measured capacitance data. Linear dependence of capacitance versus frequency reflects the depth probing of frequencies in border traps. Al-first HfAlO films with PDA show the lowest border traps density of  $4.5 \times 10^{19} \text{ cm}^{-3}$  with a barrier height 2.75 eV from the valence band edge of GaSb, confirming its smaller frequency dispersion in the accumulation region. The  $N_{bt}$  of Hf-first HfAlO films with PDA, Al-first HfAlO films without PDA are

**Figure 2.** C-V characteristics at 295 K and 10 K of Hf-first and Al-first HfAlO MOS capacitors before and after PDA.

**Figure 3.** Conductance maps for (a) as deposited Hf-first HfAlO, (b) 600°C PDA Hf-first HfAlO, (c) as deposited Al-first HfAlO, and (d) 600°C PDA Al-first HfAlO capacitors at 77 K.

$5.2 \times 10^{19} \text{ cm}^{-3}$  and  $5.6 \times 10^{19} \text{ cm}^{-3}$ , respectively. However, Hf-first HfAlO films without PDA show relatively high border traps density of  $8.2 \times 10^{19} \text{ cm}^{-3}$  with an even lower barrier height 1.91 eV from the valence band edge of GaSb. Oxygen vacancy and interstitial defects could be the source for the electron and hole traps in these high- $k$  dielectrics. Here, PDA process is proved to reduce these defects effectively.

In conclusion, we have systematically studied the CV characteristics of GaSb p-type MOS capacitors with HfAlO as gate dielectric. Al-first HfAlO is found to yield lower gate leakage, sharper transition from accumulation to depletion, and lower frequency dispersion in accumulation region than Hf-first HfAlO. The  $D_{it}$  distribution and border trap density  $N_{bt}$  at HfAlO/GaSb are quantitatively measured, which accurately explains the CV characteristics of HfAlO/GaSb MOS ca-

**Figure 4.** (a) Interface trap density ( $D_{it}$ ) distribution from near valence band edge to mid-gap for Hf-first and Al-first HfAlO on p-type GaSb before and after PDA (b) Normalized accumulation capacitance at temperature of 10 K and gate voltage of 3.9 V versus frequency (dots) and modeled results (lines) for Hf-first and Al-first HfAlO films before and after PDA.

pacitors. The PDA process on HfAlO/GaSb system is found to allow a tradeoff between interface quality and border trap density which requires further study and optimization.

The authors would like to thank A. T. Neal, J. Y. Zhang, and K. Xu for valuable discussions and N. J. Conrad for critical reading of the manuscript. This work at Purdue University is supported by the SRC Cross-Disciplinary Semiconductor Research Program and National Science Foundation. C. Wang is supported by China Scholarship Council.

## References

1. Y. Xuan, Y. Q. Wu, and P. D. Ye, *IEEE Electron Device Lett.*, **29**, 294 (2008).

2. H.-C. Chin, X. Liu, X. Gong, and Y.-C. Yeo, *IEEE Trans. Electron Devices*, **57**, 973 (2010).

3. T. Yang, Y. Xuan, D. Zemlyanov, T. Shen, Y. Q. Wu, J. M. Woodall, P. D. Ye, F. S. Aguirre-Tostado, M. Milojevic, S. McDonnell, and R. M. Wallace, *Appl. Phys. Lett.*, **91**, 142122 (2007).

4. C.-H. Chang, Y.-K. Chiou, Y.-C. Chang, K.-Y. Lee, T.-D. Lin, T.-B. Wu, M. Hong, and J. Kwo, *Appl. Phys. Lett.*, **89**, 242911 (2006).

5. G. Brammertz, H.-C. Lin, M. Caymax, M. Meuris, M. Heyns, and M. Passlack, *Appl. Phys. Lett.*, **95**, 202109 (2009).

6. Y.-T. Chen, H. Zhao, Y. Wang, F. Xue, F. Zhou, and J. C. Lee, *Appl. Phys. Lett.*, **96**, 103506 (2010).

7. M. Radosavljevic, B. Chu-Kung, S. Corcoran, G. Dewey, M. K. Hudait, J. M. Fastenau, J. Kavalieros, W. K. Liu, D. Lubyshev, M. Metz, K. Millard, N. Mukherjee, W. Rachmady, U. Shah, and R. Chau, in *IEDM Tech. Dig.* 319 (2009).

8. Y. Q. Wu, W. K. Wang, O. Koybasi, D. N. Zakharov, E. A. Stach, S. Nakahara, J. C. M. Hwang and P. D. Ye, *IEEE Electron Device Lett.*, **30**, 700 (2009).

9. J. J. Gu, Y. Q. Wu and P. D. Ye, *Journal of Appl. Phys.*, **109**, 053709 (2011).

10. M. Passlack, J. K. Abrokawah, R. Droopad, Z. Y. Yu, C. Overgaard, S. I. Yi, M. Hale, J. Sexton, and A. C. Kummel, *IEEE Electron Device Lett.*, **23**, 508 (2002).

11. A. Ali, H. S. Madan, A. P. Kirk, D. A. Zhao, D. A. Mourey, M. K. Hudait, R. M. Wallace, T. N. Jackson, B. R. Bennett, J. B. Boos, and S. Datta, *Appl. Phys. Lett.*, **97**, 143502 (2010).

12. A. Nainani, T. Irisawa, Z. Yuan, Y. Sun, T. Krishnamohan, M. Reason, B. R. Bennett, J. B. Boos, M. G. Ancona, Y. Nishi, and K. C. Saraswat, in *IEDM Tech. Dig.*, 138 (2010).

13. M. Xu, R. Wang, and P. D. Ye, *IEEE Electron Devices Lett.*, **32**, 488 (2011).

14. Available online: <http://www.ioffe.ru/SVA/NSM/Semicond/GaSb/bandstr.html>

15. P. D. Ye, *J. Vac. Sci. Technol. A*, **26**, 697 (2008).

16. P. D. Ye, Y. Xuan, Y. Q. Wu, and M. Xu, Chapter 6 on *Fundamentals of III-V Semiconductor MOSFETs*, edited by S. Oktyabrisky and P. D. Ye, published by Springer in February 2010 (ISBN: 978-1-4419-1546-7).

17. J. Robertson, *Appl. Phys. Lett.*, **94**, 152104 (2009).

18. G. D. Wilk and D. A. Muller, *Appl. Phys. Lett.*, **83**, 3984 (2003).

19. H. Hu, S. J. Ding, H. F. Lim, C. X. Zhu, M. F. Li, S. J. Kim, X. F. Yu, J. H. Chen, Y. F. Yong, B. J. Cho, D. S. H. Chan, S. C. Rustagi, M. B. Yu, C. H. Tung, A. Y. Du, D. My, P. D. Foot, A. Chin, and D.-L. Kwong, in *IEDM Tech. Dig.* 379 (2003).

20. S. Jakshik, U. Schroeder, T. Hecht, M. Gutsche, H. Seidl, and J. W. Bartha, *Thin Solid Films*, **425**, 216 (2003).

21. Y. Yuan, L. Wang, B. Yu, B. Shin, J. Ahn, P. C. McIntyre, P. M. Asbeck, M. J. W. Rodwell, and Y. Taur, *IEEE Electron Device Lett.*, **32**, 485 (2011).

22. M. Xu, K. Xu, R. Contreras, M. Milojevic, T. Shen, O. Koybasi, Y. Q. Wu, R. M. Wallace, and P. D. Ye, in *IEDM Tech. Dig.*, 865 (2009).

23. K. Martens, C. O. Chui, G. Brammertz, B. D. Jaeger, D. Kuzum, M. Meuris, M. M. Heyns, T. Krishnamohan, K. Saraswat, H. E. Maes, and G. Groeseneken, *IEEE Trans. Electron Devices*, **55**, 547 (2008).

24. Y. T. Hou, M. F. Li, H. Y. Yu, and D.-L. Kwong, *IEEE Electron Device Lett.*, **24**, 96 (2003).