# p 型硅 MOS 结构 Si/SiO<sub>2</sub> 界面及其附近的深能级与界面态\*

陈开茅 武兰青 彭清智

北京大学物理系, 北京 100871

刘 鸿 飞

北京有色金属研究总院, 北京 100088

1991 年 12 月 11 日收到

用深能级瞬态谱 (DLTS) 技术系统研究了 Si/SiO<sub>2</sub> 界面附近的深能级和界面态。结果表明, 在热氧化形成的 Si/SiO<sub>2</sub> 界面及其附近经常存在一个浓度很高的深能级, 它具有若干有趣的特殊性质, 例如它的 DLTS 峰高度强烈地依赖于温度, 以及当栅偏压使费密能级与界面处硅价带顶的距离明显小于深能级与价带顶的距离时, 仍然可以观测到一个很强的 DLTS 峰。另外, 用最新方法<sup>[1]</sup>测量的 Si/SiO<sub>2</sub> 界面连续态的空穴俘获截面与温度有关, 而与能量位置无明显关系。DLTS 测量的界面态能量分布与准静态 C-V 测量的结果完全不一致。本文提出的 Si/SiO<sub>2</sub> 界面物理模型能合理地解释上述问题。

PACC: 7340; 7320; 7155; 7340Q

## 一、引言

Si/SiO<sub>2</sub> 界面的局域电子态对绝缘栅场效应器件的工作性能会造成十分有害的影响。对这种界面态的深入了解将有助于通过最佳工艺最大程度地减小其影响以及预期器件的性能。在过去的 30 多年中, 已对 Si/SiO<sub>2</sub> 界面态进行过广泛的研究<sup>[1-8]</sup>。现在普遍认为这种界面态是遍布于硅禁带的连续谱, 且其密度随能量从禁带中央向带边单调地增加, 即 U 型分布<sup>[4,9]</sup>。但这种分布与绝大多数 DLTS 测量结果是不一致的<sup>[2,10]</sup>。这种不一致的原因至今未得到合理的解释。另外, 在经过低温退火的 P 型硅 MOS 结构的 DLTS 测量中, 在室温以上经常存在着一个高大的 DLTS 峰<sup>[11]</sup>。这个峰很容易被误认为是半导体表面少数载流子产生-复合或所谓切断效应<sup>[1,12-14]</sup>造成的假峰。但是只要认真详细地观测, 就可以发现它与上述效应造成的假峰不是一回事, 它确实是 Si/SiO<sub>2</sub> 界面附近的深能级所造成的。

本文详细研究了这一深能级的特殊性质, 以及用新的测量界面态俘获截面的方法<sup>[15]</sup>

\* 国家自然科学基金资助的课题。

研究 Si/SiO<sub>2</sub> 界面态的俘获性质, 用 DLTS 测量 Si 禁带下半部 Si/SiO<sub>2</sub> 界面态的分布, 并解释 DLTS 和准静态 C-V 两种技术测量结果不一致的原因。

## 二、实验与结果

这个工作的实验样品是 MOS 结构, 样品衬底是(111)晶向和电阻率为 5—8 Ω·cm 的 P 型硅单晶片。在 1050°C 的掺 1% HCl 气体的干氧气氛中, 使硅片的正面热氧化生成厚度约为 1600 Å 的氧化层。在氧化层上蒸发厚度约为 1 μm 厚的铝膜, 用光刻技术刻出直径为 1400 μm 的圆形铝电极。在硅片的背面蒸发上铝膜并在 470°C 的氮氢混合气体 (H<sub>2</sub>:N<sub>2</sub> = 1:9) 中合金化 30 min, 以便形成良好的欧姆接触。

### 1. Si/SiO<sub>2</sub> 界面附近深能级 $H_{1t}(0.494)$

经过对 MOS 结构作高频 C-V 测量和分析之后, 得知在室温时它们的平带电压  $V_{FB}$  为 -3.33 V 左右, 以及使其半导体表面处于本征态的栅压为 -2.51 V 左右。

在从 77 K 升温到室温以上的 DLTS 测量中, 为了使样品的所有界面态(只指快态)能被脉冲引进的空穴尽可能饱和地填充, 我们主要采用宽和高的脉冲, 宽度  $t_p$  在 1—30 ms 范围, 以及高度在 10—15 V 范围。

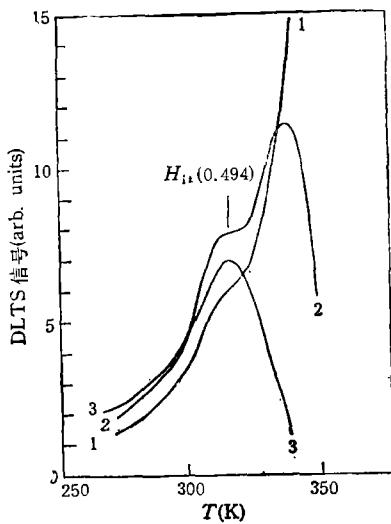

图 1 示出样品 DLTS 谱线的高温段随栅压的变化。其中谱线 1 和 2 对应于栅压使半导体表面处于反型的状态。图 1 中未示出曲线 1 所达到的高峰, 在那峰的左侧约 310 与 320 K 温度之间有一个小鼓包。谱线 2 虽然也对应于反型的情况, 但它比谱线 1 对应

图 1 经低温退火的 P 型硅 MOS 结构 DLTS 谱线随偏压的变化 脉冲  $V_p = -15V$ ,  $t_p = 1.5ms$ ; 率窗:  $t_1 = 5ms$ ,  $t_2 = 10ms$ ;  $E_F^S - E_F^D$  表示在峰温处在界面费密能级与 Si 价带顶的间距; 曲线 1, 2, 3 分别对应于栅压  $V_g$  为 -1.67, -2.12, -2.51 V 和  $E_F^S - E_F^D$  为 0.784, 0.690, 0.565 eV

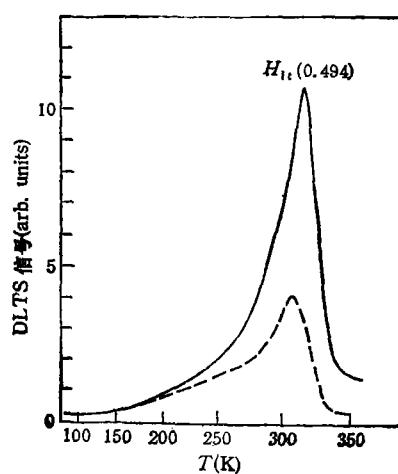

图 2 P 型硅 MOS 结构 Si/SiO<sub>2</sub> 界面态 DLTS 谱  $V_g = -2.70V$ ; 脉冲宽度  $t_p = 1.5ms$ ; 虚线和实线相应于脉冲高度  $V_p$  分别为 -2.50 V 和 -15.0 V 的谱线; 率窗:  $t_1 = 2.5ms$ ,  $t_2 = 5ms$

的反型弱, 相应地它的最高峰比谱线 1 的低得多, 而且峰的位置向低温方向移动, 同时作为它的肩膀的鼓包明显突起。这个肩膀就是  $\text{Si}/\text{SiO}_2$  界面附近的缺陷  $H_{1t}(0.494)$  对应的 DLTS 峰, 而谱线 1 和 2 的最高峰即是半导体表面层少数载流子(电子)产生-复合所造成的假峰<sup>[1,12]</sup>。图 1 中的谱线 3 对应于栅压使半导体表面处于本征状态。在这一谱线中, 不存在半导体表面少数载流子产生-复合造成的假峰, 从而清晰地显出  $H_{1t}(0.494)$  对应的峰。

应该指出, 如果栅压使半导体表面的反型比谱线 1 对应的情况更严重, 则  $H_{1t}(0.494)$  对应的峰将完全被假峰所埋没, 人们观测不到。还应指出, 在栅压使半导体表面处于从本征态到多数载流子累积状态的范围内, 不存在假峰。

图 2 示出栅压为  $-2.70 \text{ V}$ (相应地在  $300 \text{ K}$  时, 在  $\text{Si}/\text{SiO}_2$  界面处费密能级  $E_F^*$  与  $\text{Si}$  价带顶  $E_V^*$  的间距  $E_F^* - E_V^* = 0.452 \text{ eV}$ ) 时, P 型硅 MOS 结构  $\text{Si}/\text{SiO}_2$  界面态从  $77 \text{ K}$  到室温以上的完整的 DLTS 谱。由图 2 可见,  $H_{1t}(0.494)$  的峰最为突出, 它是  $\text{Si}/\text{SiO}_2$  界面及其附近的主缺陷, 其 DLTS 峰高强烈地依赖于脉冲高度  $V_p$ 。

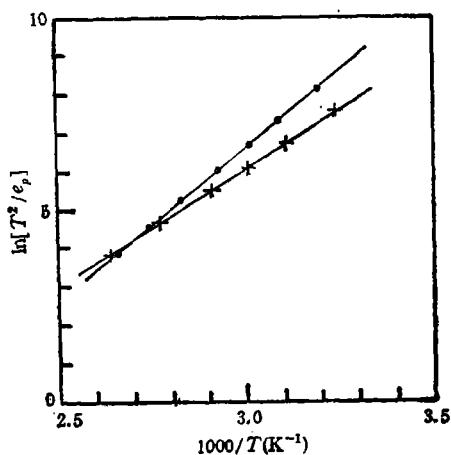

图 3 示出  $H_{1t}(0.494)$  的空穴热发射率  $\epsilon_p$  与温度  $T$  的关系。其中叉号数据是样品栅压为  $-2.61 \text{ V}$ (对应于  $320 \text{ K}$  时,  $E_F^* - E_V^* = 0.504 \text{ eV}$ ) 以及脉冲高度为  $-0.72 \text{ V}$ (此时脉冲恰好使半导体表面处于平带状态)时测量的结果。将这些数据用最小二乘法配成为

$$\epsilon_p = 1.6 \times 10^5 T^2 \exp\left(-\frac{0.519 \text{ eV}}{kT}\right) \quad (\text{s}^{-1}), \quad (1)$$

其中  $0.519 \text{ eV}$  为  $H_{1t}(0.494)$  的空穴表观激活能。图 2 中的另一组数据是栅压为  $-3.10 \text{ V}$ (相应于  $E_F^* - E_V^* = 0.311 \text{ eV}$ ) 以及脉冲高度为  $-10.0 \text{ V}$  的测量结果。由图 2 可见, 两条曲线的线性行为是比较好的。这说明在  $H_{1t}(0.494)$  的空穴发射过程中, 很少有隧道效应的影响<sup>[16-19]</sup>, 发射是热激发的结果。除上述之外,  $H_{1t}(0.494)$  还具有如下有趣的特

图 3  $H_{1t}(0.494)$  空穴热发射率与温度的关系 “+”代表  $V_g = -2.61 \text{ V}$ ,  $V_p = -0.72 \text{ V}$ ,  $t_p = 5 \text{ ms}$  时的数据; “●”表示  $V_g = -3.10 \text{ V}$ ,  $V_p = -10.0 \text{ V}$ ,  $t_p = 5 \text{ ms}$  时的数据

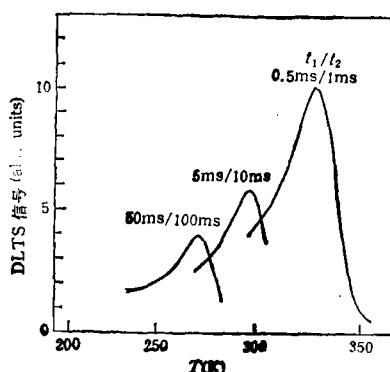

图 4  $H_{1t}(0.494)$  的 DLTS 峰高度与率窗的关系  $V_g = -2.84 \text{ V}$ ;  $V_p = -15.0 \text{ V}$ ;  $t_p = 1.5 \text{ ms}$

点:

(1) 它的 DLTS 峰高强烈地依赖于温度

图 4 示出当 MOS 结构的栅压为 -2.84 V (对应于 320 K 时,  $E_F^* - E_V^* = 0.390 \text{ eV}$ ) 时,  $H_{it}(0.494)$  的 DLTS 峰高与取样时间  $t_1$  和  $t_2$  的关系。在实验中取  $t_1/t_2 = 1/2$ , 当  $t_2$  从 100 ms 缩短到 1 ms 时,  $H_{it}(0.494)$  峰高增加了 1.5 倍。率窗决定着 DLTS 峰的位置(温度), 峰高与率窗的关系实质上反映的是峰高与温度的关系。

(2)  $H_{it}(0.494)$  空穴填充的不饱和性

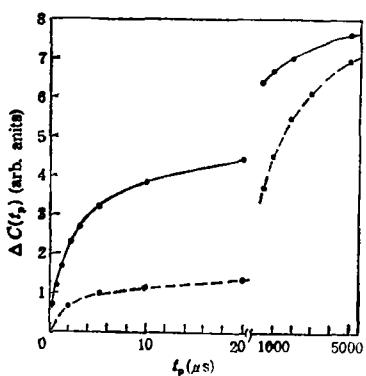

图 5 示出 Si/SiO<sub>2</sub> 界面附近主缺陷  $H_{it}(0.494)$  的空穴填充过程。从图 5 中看出, 当脉冲宽度增至 5000 μs 时,  $H_{it}(0.494)$  仍然未被脉冲引进的空穴饱和填充。另外从  $\Delta C(t_p)$  随脉冲宽度  $t_p$  的变化趋势看出,  $H_{it}(0.494)$  的空穴填充包含着从快俘获到慢俘获的多种填充过程, 即  $\Delta C(t_p)$  是由许多长短不同的时间常数的指数时间函数组成的。图 5 中的实线(对应于 320 K 时  $E_F^* - E_V^* = 0.504 \text{ eV}$ ,  $V_g = -0.72 \text{ V}$ , 脉冲恰好使半导体表面处于平带状态)包含着比较多的快俘获成份。而相比之下, 虚线(对应于 320 K 时,  $E_F^* - E_V^* = 0.311 \text{ eV}$ ,  $V_g = -10.0 \text{ V}$ , 在脉冲期间半导体表面处于多数载流子强累积状态)包含的快俘获成份明显地减少, 它主要包含的是慢俘获成份。这种填充的多指数瞬态和半导体空间电荷区边区中的深中心的多数载流子填充是类似的<sup>[20,21]</sup>。但是可以证明  $H_{it}(0.494)$  不是分布于半导体内部的深能级, 而是 Si/SiO<sub>2</sub> 界面附近的缺陷(见后面)。

图 5  $H_{it}(0.494)$  的电容瞬态初值  $\Delta C(t_p)$  与脉冲宽度  $t_p$  的关系 实线:  $V_g = -2.61 \text{ V}$ ,  $V_p = -0.72 \text{ V}$ ; 虚线:  $V_g = -3.10 \text{ V}$ ,  $V_p = -10.0 \text{ V}$ ;  $T = 320 \text{ K}$

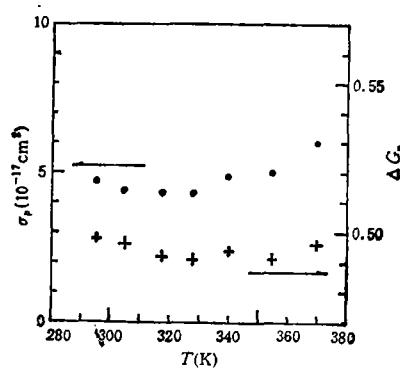

图 6  $H_{it}(0.494)$  的空穴俘获截面和空穴离化吉布斯自由能与温度的关系  $V_g = -2.61 \text{ V}$ ,  $V_p = -0.72 \text{ V}$ , “●”表示俘获截面  $\sigma_p$ ; “+”表示自由能;  $\Delta G_p$  的单位为 eV

(3)  $H_{it}(0.494)$  的空穴离化吉布斯自由能  $\Delta G_p$

文献[22—24]指出表征深能级在半导体禁带中位置的物理量应该是离化吉布斯自由能。根据图 3 中叉号所示的空穴热发射率和由空穴俘获过程测量的空穴俘获截面  $\sigma_p$  (见图 6 中的实心圆点表示的数据)以及 Engström 的公式<sup>[23]</sup>:

$$\epsilon_p = \sigma_p \langle V_p \rangle N_v \exp(-\Delta G_p/kT), \quad (2)$$

可以求出  $H_{it}(0.494)$  的空穴离化吉布斯自由能  $\Delta G_p$ , 见图 6 中的叉号表示的数据, 它是随温度变化的。在 310—380 K 的测量温度范围内, 它的平均值为 0.494 eV。据此将所

表 1  $H_{it}(0.494)$  面密度  $D_H$  与  $E_F^* - E_v^*$  的关系 ( $V_p = -15.0V$ )

|                                  |       |       |       |       |       |       |       |       |       |

|----------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| $E_F^* - E_v^*$ (eV)             | 0.162 | 0.214 | 0.240 | 0.226 | 0.318 | 0.370 | 0.421 | 0.473 | 0.525 |

| $D_H$ ( $10^4 \text{ cm}^{-2}$ ) | 1.13  | 4.60  | 4.48  | 13.5  | 30.4  | 53.3  | 74.3  | 89.9  | 100.8 |

研究的界面缺陷记为  $H_{it}(0.494)$ 。

#### (4) 一个新奇的特性

图 7 示出在不同栅压条件下, 电压脉冲把 MOS 结构推进强累积状态以及脉冲过后

所观测的  $H_{it}(0.494)$  的 DLTS 峰。从图 7 中看到, 在栅压使  $E_F^* - E_v^*$  小于  $H_{it}(0.494)$  的空穴离化吉布斯自由能, 甚至小于 0.288 eV (在 300 K 温度、半导体表面处于平带时费密能级与 Si 价带顶的间距) 时, 仍然可以观测到  $H_{it}(0.494)$  的大峰, 峰高随  $E_F^* - E_v^*$  的减小而降低。表 1 定量地给出 DLTS 测量的  $H_{it}(0.494)$  的面密度  $D_H$  随  $E_F^* - E_v^*$  的变化。

从 DLTS 测量原理知道, 对于 P 型半导体, 如果直流偏置已使被测深中心全都处于费密能级之上, 则这些深中心不会再为脉冲引进的空穴所填充, 因为它们原来已经变空, 这样也就不会有它们的 DLTS 信号出现。但这一推论与实验事实不符, 故图 7 和表 1 所测的  $H_{it}(0.494)$  不是半导体中的深中心。

同理, 如果按照目前的多数人看法, 把硅 MOS 结构的能带结构看成是在  $\text{Si}/\text{SiO}_2$  界面处从硅单晶的能带突然跃变到  $\text{SiO}_2$  的能带, 则

当  $E_F^* - E_v^*$  小于  $H_{it}(0.494)$  的空穴离化吉布斯自由能时, 也不会有  $H_{it}(0.494)$  的 DLTS 信号。这一推论同样与图 7 和表 1 的实验事实不符, 因此能带跃变的看法可能是不对的。

#### (5) $H_{it}(0.494)$ 的空穴表观激活能随 $E_F^* - E_v^*$ 的变化

从图 7 还看到  $H_{it}(0.494)$  的 DLTS 峰位置随着  $E_F^* - E_v^*$  的减小而移向更高的温度。这就意味着  $H_{it}(0.494)$  的空穴表观激活能随  $E_F^* - E_v^*$  的缩小而增大。表 2 具体

表 2  $H_{it}(0.494)$  空穴表观激活能与  $E_F^* - E_v^*$  的关系 ( $V_p = -10.0V$ )

|                      |       |       |       |       |       |

|----------------------|-------|-------|-------|-------|-------|

| $E_F^* - E_v^*$ (eV) | 0.547 | 0.452 | 0.370 | 0.311 | 0.267 |

| 表观激活能 (eV)           | 0.539 | 0.579 | 0.649 | 0.700 | 0.746 |

地说明了这种情况。

## 2. p型硅 Si/SiO<sub>2</sub> 界面态的连续谱

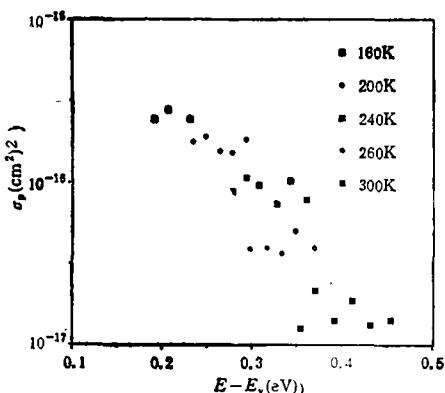

在图 2 示出的 DLTS 谱中, 温度低于 250 K 的那一部分主要是 Si/SiO<sub>2</sub> 界面连续态的贡献。我们用最近提出的准确测量俘获截面的方法<sup>[15]</sup>测量了这种连续态的空穴俘获截面  $\sigma_p(E, T)$ , 图 8 示出这一测量结果。从图 8 中可知, 对于每一恒定温度, 界面态的空穴俘获截面与能量无明显关系; 对于每一已知能量, 空穴俘获截面随温度降低而增大。经过对这些数据的进一步分析, 得到 Si/SiO<sub>2</sub> 界面连续态的空穴俘获截面与温度的关系可近似地表示为

$$\sigma_p = 2.5 \times 10^{-17} \left( \frac{300}{T} \right)^{3.9} \text{ (cm}^2\text{).} \quad (3)$$

在得知界面态的俘获截面与能量和温度的关系之后, 人们就可以把界面态的 DLTS 谱反演成为界面态的能量分布。界面态的 DLTS 谱与能量分布之间的换算公式为<sup>[10]</sup>

$$D_{it}(E) = -A\epsilon_{Si}N_A C_{ox} [\Delta C(t_1) - \Delta C(t_2)] / C^3(V_g) kT \ln 2, \quad (4)$$

其中  $D_{it}(E)$  为能量  $E$  处单位面积单位能量的界面态, 以及

$$E = kT \ln [\sigma_p v_p N_v t_1 / \ln 2], \quad (5)$$

$\epsilon_{Si}$  为硅的介电常数,  $N_A$  为半导体中的浅受主浓度,  $C_{ox}$  为 MOS 结构的氧化层电容,  $C(V_g)$  为栅压  $V_g$  对应的 MOS 结构电容,  $A$  为 MOS 结构的面积,  $k$  为波耳兹曼常数,  $\Delta C(t_1) - \Delta C(t_2)$  为 DLTS 信号,  $v_p$  为空穴的热运动速度,  $N_v$  为 Si 价带有效状态密度。

图 8 p型硅 MOS 结构 Si/SiO<sub>2</sub> 界面连续态的空穴俘获截面与能量和温度的关系

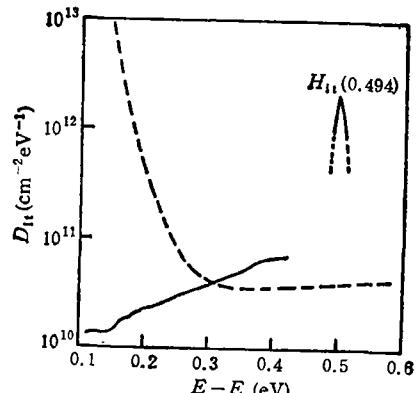

图 9 经低温退火的 MOS 结构 Si/SiO<sub>2</sub> 界面的能量分布 实线和虚线分别表示 DLTS 和准静态 C-V 的测量结果

利用(3)–(5)式, 将图 2 的 DLTS 谱计算成为界面态的能量分布, 见图 9 中的实线。为了便于比较, 把同一样品的准静态 C-V 测量的结果也绘在图 9 中。从图 9 中看出两种技术测量的结果是很不一致的。DLTS 测量的结果是在价带以上 0.4 eV 左右, 界面态密度比较大, 约为  $7 \times 10^{10} \text{ cm}^{-2} \text{ eV}^{-1}$ , 接着态密度向价带方向几乎是单调地衰减。相反,

准静态  $C-V$  的测量结果是在硅禁带中央附近,界面态密度比较小,而且近于常数分布,密度约为  $4 \times 10^{10} \text{ cm}^{-2} \text{ eV}^{-1}$ ,接着态密度向价带方向急剧增大。应该指出在准静态  $C-V$  测量结果中丝毫看不出  $H_{it}(0.494)$  的存在。

### 三、讨 论

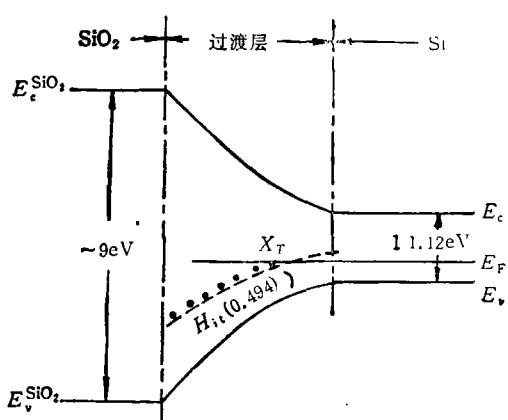

第二节的测量结果揭示出  $\text{Si}/\text{SiO}_2$  界面附近深中心  $H_{it}(0.494)$  的若干特殊性质,以及 DLTS 和准静态  $C-V$  两种技术测量的  $\text{Si}/\text{SiO}_2$  界面态能量分布的严重差异。这些都是需要认真解释和讨论的,为此我们提出包含  $H_{it}(0.494)$  缺陷在内的  $\text{Si}/\text{SiO}_2$  界面物理模型,见图 10。该模型包含下述两个要点。(1) 在单晶硅与  $\text{SiO}_2$  之间存在着一个不宽的能带过渡区。(2)  $H_{it}(0.494)$  分布在过渡区中,它的能级与价带顶的距离  $\Delta G$ ,随着离开单晶半导体表面而增大。下面用此模型讨论第二节中的结果。

对 MOS 结构加上适当的栅压使半导体表面耗尽时, P 型硅半导体表面的能带向下弯曲,同时位于过渡区不同位置的  $H_{it}(0.494)$  的能级跟着下降。当所加栅压使所有的  $H_{it}(0.494)$  低于费密能级  $E_F$  时,  $H_{it}(0.494)$  全部为电子填充。如果电压脉冲只使半导体表面处于平带状态,则只有处在从半导体表面到费密能级  $E_F$  与  $H_{it}(0.494)$  能级交点  $X_T$  的这一部分过渡区中的  $H_{it}(0.494)$  能移到费密能级之上,并被脉冲引进的空穴填充和产生电容瞬态信号。由于  $\text{Si}/\text{SiO}_2$  界面过渡区价带下弯,致使价带的空穴浓度分布很不均匀,即在单晶硅半导体表面,空穴浓度最大,约等于半导体内部的空穴浓度,而在  $X_T$  附近空穴浓度很低。相应地,不同部位的  $H_{it}(0.494)$  对空穴的俘获率也很不相同,这就造成  $H_{it}(0.494)$  的电容瞬态初值  $\Delta C(t_p)$  是脉冲宽度  $t_p$  的多指数函数,并且表现为  $\Delta C(t_p)$  很难通过增大脉冲宽度而达到其饱和值,见图 5 中的实线。

图 10  $\text{Si}/\text{SiO}_2$  界面物理模型示意

从图 10 看到,若  $H_{it}(0.494)$  确实分布在过渡区中,并且它们的能级位置随着价带下弯而降低,则当栅压使  $E_F^* - E_v^*$  小于  $H_{it}(0.494)$  的空穴离化吉布斯自由能,甚至小于 0.228 eV (半导体表面处于平带时对应的  $E_F^* - E_v^*$  值)时,也还有相当多的  $H_{it}(0.494)$  处于费密能级以下,在多子脉冲的作用下,它们有可能产生 DLTS 信号,而且随着  $E_F^* - E_v^*$  的减小这个信号是减小的。这就是图 7 和表 1 所示的结果。

从图 10 中还看到,如果  $H_{it}(0.494)$  的能级不平行于价带,而是随着离开单晶半导体表面的距离的增大而逐步偏离价带,则随着  $E_F^* - E_v^*$  的减小,能被脉冲引进的空穴填充的  $H_{it}(0.494)$  离开半导体表面越远,它们的空穴离化吉布斯自由能就越大,相应地  $H_{it}(0.494)$  的 DLTS 峰就越向高温方向移动,它们的表观激活能就越大。这就是图 7 和表 2 所示的结果。

在某一给定栅压和一定的电压脉冲推动下,  $H_{it}(0.494)$  的 DLTS 峰高强烈地依赖于温度(见图 4)的关系, 主要是由于温度升高使费密能级向禁带中央移动造成的。就图 4 所用样品而言, 当温度从 270 K 升高到 340 K 时, 费密能级向硅禁带中央移动了 60 meV。由图 10 可知, 这就导致了随温度升高有更多的  $H_{it}(0.494)$  被脉冲引进的空穴填充, 从而产生更高的 DLTS 峰。

图 9 示出同一 MOS 样品的 DLTS 测量的界面态分布和准静态 C-V 测量结果严重不一致, 其主要原因如下:

(1) 准静态 C-V 技术表征的是界面态在半导体禁带中的分布, 而 DLTS 技术表征的是界面态密度随激活能的变化。因此象 Si/SiO<sub>2</sub> 界面物理模型所示的  $H_{it}(0.494)$  缺陷, 在 DLTS 测量中, 表现为离散或类离散能级, 而在准静态 C-V 技术测量中, 它们被视为分布在硅禁带中央到价带中的连续界面态。这就是准静态 C-V 测量的 Si/SiO<sub>2</sub> 界面态密度在价带边大大高于 DLTS 测量的原因之一。

(2) 准静态 C-V 测量的是快界面态和慢界面态之和, 而 DLTS 测量的主要快界面态。

(3) 对于俘获截面非常小的界面态, 很难产生 DLTS 信号, 不能用 DLTS 技术测量, 而准静态 C-V 对俘获截面并不那么敏感。

从第二节的测量结果以及上述分析看出,  $H_{it}(0.494)$  是 Si/SiO<sub>2</sub> 界面附近的主要缺陷也是重要深能级。其重要性主要来自两方面, 其一它是经低温退火后仍然存在着的缺陷, 它位于硅禁带中央附近, 且密度相当高, 它可能对 MOS 器件 Si/SiO<sub>2</sub> 界面的少数载流子产生-复合有决定性的影响; 其二它具有若干有趣的特殊性质, 利用它有可能进一步研究 Si/SiO<sub>2</sub> 界面的物理性质。关于  $H_{it}(0.494)$  缺陷的起源及其化学组成以及微观结构, 本文未作探讨, 有待以后研究。

#### 四、结 论

$H_{it}(0.494)$  是一个基本的、重要的 Si/SiO<sub>2</sub> 界面及其附近的深能级, 它具有若干特殊性质: 它的 DLTS 峰高度强烈地依赖于温度; 它很难为脉冲引进的空穴饱和填充; 它的平均空穴离化吉布斯自由能为 0.494 eV; 当栅压使  $E_F^* - E_V^* < 0.494$  eV 时, 仍然可以观测到它的很强的 DLTS 峰; 它的表观激活能随  $E_F^* - E_V^*$  的减小而增大。我们提出的包含  $H_{it}(0.494)$  的 Si/SiO<sub>2</sub> 界面物理模型能合理地解释上述各种问题。

p型硅 MOS 结构 Si/SiO<sub>2</sub> 界面态的空穴俘获截面与温度有关, 其典型值为  $3 \times 10^{-17}$  cm<sup>2</sup>。据此我们推测在硅禁带下半部的界面态是施主态。

在这工作中, 作者曾与北京师范大学卢世通先生作过多次有益的讨论, 北京半导体器件五厂朱秀兰同志为我们提供了测试样品。在此对他们表示感谢!

- [1] N. M. Johnson, D. J. Bartelink and M. Schulz, in *The Physics of SiO<sub>2</sub> and Its Interfaces*, edited by S. T. Pantelides, (Pergamon, New York, 1978), p. 421.

- [2] M. Schulz, *Surf. Sci.*, **132**(1983), 422.

- [3] K. L. Wang, *IEEE Trans. Electron Devices*, **ED-26**(1979), 819.

- [4] C. T. Sah, J. Y. C. Sun and J. J. T. Tzou, *J. Appl. Phys.*, **53**(1982), 8886.

- [5] C. T. Sah, J. Y. C. Sun and J. J. T. Tzou, *J. Appl. Phys.*, **54**(1983), 4378.

- [6] H. Deuling, E. Klausmann and A. Goetzberger, *Solid State Electron.*, **15**(1972), 559.

- [7] E. H. Poindexter, G. J. Gerardi, M.-E. Ruechel, P. J. Caplan, N. M. Johnson and D. K. Biegelsen, *J. Appl. Phys.*, **56**(1984), 2844.

- [8] D. Vuillaume, R. Bouchakour, M. Jourdain and J. C. Bourgoin, *Appl. Phys. Lett.*, **55**(1989), 153.

- [9] A. Goetzberger, E. Klausmann and M. Schulz, CRC Critical Review, 1(Jan. 1976), and references listed therein.

- [10] K. M. Chen, Z. A. Wang, C. G. Fong, Q. Zhang, and Y. X. Gao, *Chinese Physics*, **5**(1985), 489.

- [11] K. M. Chen and D. T. Lu, *Science in China*, **A32**(1989), 1458.

- [12] N. M. Johnson, *J. Vac. Sci. Technol.*, **21**(1982), 303.

- [13] E. Rosencher and R. Coppard, *J. Appl. Phys.*, **55**(1984), 971.

- [14] D. Vuillaume and J. C. Bourgoin, *J. Appl. Phys.*, **58**(1985), 2077.

- [15] 陈开茅、武兰青、许惠英、刘鸿飞,中国科学(A辑)待发表。

- [16] G. Vincent, A. Chantre and D. Bois, *J. Appl. Phys.*, **50**(1979), 5484.

- [17] D. Pons and S. Makram-Ebeid, *J. Phys. Theor. Appl.*, **40**(1979), 1161.

- [18] P. A. Martin, B. G. Streetman and K. Hess, *J. Appl. Phys.*, **52**(1981), 7409.

- [19] D. Vuillaume, J. C. Bourgoin and M. Lannoo, *Phys. Rev.*, **B34**(1986), 1171.

- [20] A. Zylbersztejn, *Appl. Phys. Lett.*, **33**(1978), 200.

- [21] 陈开茅、秦国刚、王忠安、金泗轩,物理学报,33,(1984),486.

- [22] H. Brooks, Advances in Electronics and Electron Physics, Ed. L. Marton (Academic Press Inc. Publishers, New York, 1955), Vol. VII p. 17.

- [23] O. Engström and A. Alm, *Solid State Electron.*, **21**(1978), 1571.

- [24] K. M. Chen and G. G. Qin, *Chinese Physics*, **7**(1987), 1110.

# DEEP LEVEL IN BOTH Si/SiO<sub>2</sub> INTERFACE AND ITS NEIGHBOURHOOD AND Si/SiO<sub>2</sub> INTERFACE STATES IN p TYPE SILICON MOS STRUCTURE

CHEN KAI-MAO WU LAN-QING PENG QING-ZHI

*Department of Physics, Peking University, Beijing 100871*

LIU HONG-FEI

*General Research Institute for Non-ferrous Metal, Beijing 100088*

(Received 11 December 1991)

## ABSTRACT

The deep level in both Si/SiO<sub>2</sub> interface and its neighbourhood and Si/SiO<sub>2</sub> interface states have been studied systematically with Deep Level Transient Spectroscopy (DLTS). Experimental results show that a dominant deep level,  $H$  (0.494), exists in both Si/SiO<sub>2</sub> interface and its neighborhood in MOS structure formed by thermal oxidation. The deep level possesses some interesting properties, for example, its DLTS peak height depends strongly on temperature, and when the gate voltage reduces the interval between Fermi-level and Si valence band to a value less than that between the deep level and Si valence band, its sharp DLTS peak is still observable. The hole capture cross section of the interface states at Si/SiO<sub>2</sub> interface has been found to depend on temperature, measured with a new method<sup>[1]</sup>. The energy distribution of the interface states measured with DLTS contradicts to the distribution obtained by quasistatic C-V technique. A new physical model of Si/SiO<sub>2</sub> interface was proposed. with this model the above stated experimental results can be successfully expounded.

**PACC:** 7340; 7320; 7155; 7340Q