# Impact of Forming Gas Annealing and Firing on the $\text{Al}_2\text{O}_3/\text{p-Si}$ Interface State Spectrum

E. Simoen,<sup>a,\*</sup> A. Rothschild,<sup>a</sup> B. Vermang,<sup>a,b</sup> J. Poortmans,<sup>a,b</sup> and R. Mertens<sup>a,b</sup>

<sup>a</sup>imec, B-3001 Leuven, Belgium

<sup>b</sup>EE Department, KU Leuven, B-3001 Leuven, Belgium

The interface-state spectrum at the  $\text{Al}_2\text{O}_3/\text{p-Si}$  interface is investigated by Deep-Level Transient Spectroscopy on Metal-Oxide-Semiconductor (MOS) capacitors. It is shown that a Forming Gas Anneal or firing step leads to a significant reduction of the density of interface states ( $D_{it}$ ). At the same time, it is found that the peak activation energy of the  $D_{it}$  distribution lowers towards the valence band of Si. From a comparison with the DLTS data on 5 nm  $\text{SiO}_2$  MOS capacitors, it is concluded that the same type of states is observed for both dielectrics, implying that the interface properties are determined by the thin interfacial  $\text{SiO}_2$  layer.

© 2011 The Electrochemical Society. [DOI: 10.1149/1.3597661] All rights reserved.

Manuscript submitted March 30, 2011; revised manuscript received May 13, 2011. Published June 10, 2011.

One of the first so-called high-k dielectrics that received considerable research interest from the Complementary Metal-Oxide-Semiconductor (CMOS) scaling community was  $\text{Al}_2\text{O}_3$ .<sup>1,2</sup> When screening high-k materials for the fabrication of Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs),  $\text{Al}_2\text{O}_3$  appears to be a good candidate because of its excellent dielectric properties – a high band gap and a reasonable high k value – its strong adhesion to dissimilar materials and its thermal and chemical stability. This explains the strong research interest in the interface and trapping properties of the  $\text{Al}_2\text{O}_3/\text{Si}$  system at some point in time.<sup>3–5</sup> Meanwhile, it has become clear that for device scaling alternative high-k materials offer better perspectives, but at the same time,  $\text{SiO}_2/\text{Al}_2\text{O}_3$  bilayer stacks can also be employed for the development of non volatile memories.<sup>6,7</sup> Quite recently, it has been demonstrated that the negative fixed oxide charge in  $\text{Al}_2\text{O}_3$  is favorable for reaching a good field-induced surface passivation of p-type silicon for solar cell applications.<sup>8–10</sup> This has triggered quite some investigations on the electrical properties of the  $\text{Al}_2\text{O}_3/\text{Si}$  system<sup>11–17</sup> and it has been pointed out that both chemical and field-effect passivation play a role in the improvement of the surface recombination properties.<sup>8–10,18,19</sup> A related point of interest is whether the density of interface states ( $D_{it}$ ) can be reduced by hydrogen passivation, using for example a post-Al-metallization Forming Gas Anneal (FGA).<sup>20–22</sup> At the same time, one should address the question of the stability of the  $\text{Al}_2\text{O}_3$  properties under a high temperature firing process, which is typically applied between 700 and 850°C.<sup>20</sup>

The present work investigates the interface properties of  $\text{Al}/\text{Al}_2\text{O}_3/\text{p-Si}$  Metal-Oxide-Semiconductor (MOS) capacitors after various processing steps, namely, as-deposited, after a 30 min FGA (10%  $\text{H}_2$  in  $\text{N}_2$ ) at 350°C and after a firing step, consisting of a Rapid Thermal Processing (RTP) with a peak temperature above 800°C for 1–2 s.<sup>23</sup> The FGA and firing steps have been applied after Al gate deposition. Initial results on the surface recombination properties have been recently reported.<sup>24</sup> Deep-Level Transient Spectroscopy (DLTS) is used to generate a  $D_{it}$  distribution versus activation energy with respect to the valence band edge  $E_V$ . Earlier studies on Atomic Layer Deposited (ALD) 5.8-nm thick  $\text{Al}_2\text{O}_3$  layers revealed deep-level peaks at 0.19, 0.24, 0.29 and 0.37 eV, respectively.<sup>25</sup> At the same time, it was observed that a FGA at 450°C reduced the  $D_{it}$  significantly from  $10^{12} \text{ cm}^{-2} \text{ eV}^{-1}$  to  $4 \times 10^{11} \text{ cm}^{-2} \text{ eV}^{-1}$  at  $E_V + 0.35$  eV. It is shown here that both FGA and firing of 5 nm  $\text{Al}_2\text{O}_3$  layers result in a clear reduction of the  $D_{it}$ , whereby also the activation energy, corresponding with the DLTS peak maximum reduces. A similar behavior is observed for 5 nm thermal  $\text{SiO}_2$  reference samples, indicating that the observed interface states are related with the thin interfacial  $\text{SiO}_2$  layer which is formed upon  $\text{Al}_2\text{O}_3$  deposition.

Before deposition, the 200 mm diameter p-type Czochralski Si substrates were cleaned in a hot  $\text{H}_2\text{O}_2:\text{H}_2\text{SO}_4$  1:4 solution, followed by an HF-dip and a water rinse. Forty cycles of ALD  $\text{Al}_2\text{O}_3$  was performed in a Savannah tool at 200°C, with  $\text{H}_2\text{O}$  as the oxygen precursor and trimethyl-aluminum (TMA) as the Al precursor, resulting in a thickness of 5 nm. The pulsing sequence was  $\text{H}_2\text{O}$ , TMA,  $\text{H}_2\text{O}$ . This was followed by the sputtering of 500 nm thick Al gate electrodes with different diameters. The 5 nm  $\text{SiO}_2$  reference capacitors were fabricated using *in-situ* steam generated oxidation at 850°C.

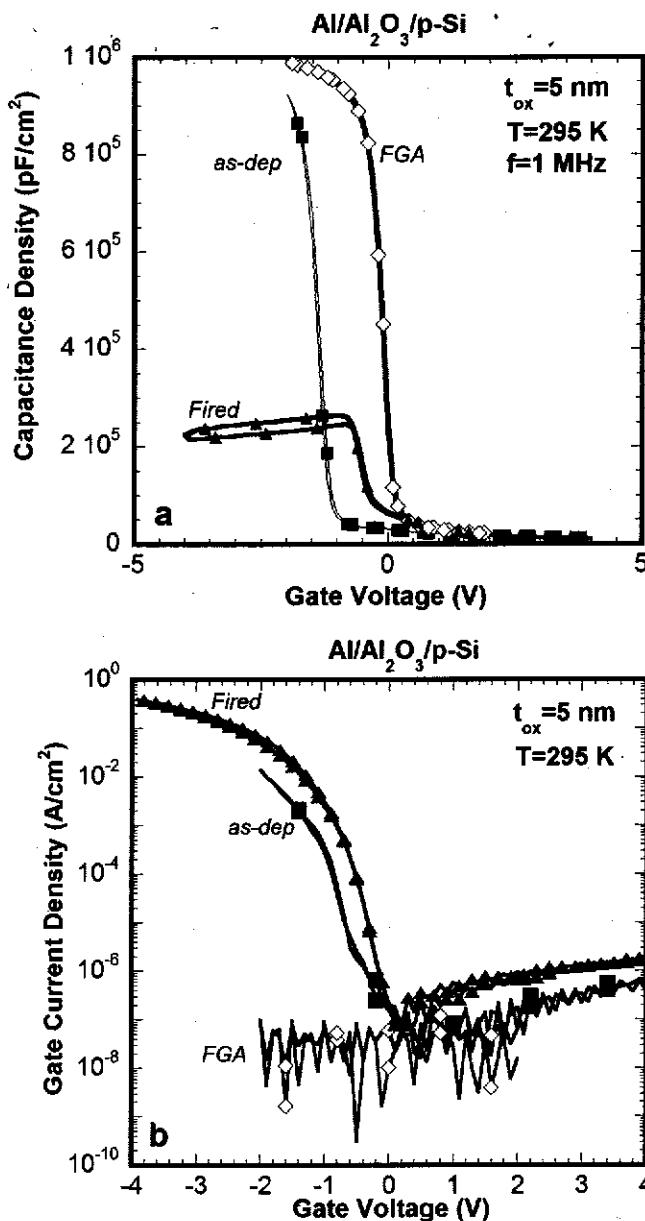

Before DLTS, 1 MHz Capacitance-Voltage (C-V) and Current-Voltage (I-V) measurements have been performed at room temperature in order to define a proper bias-pulse range for the DLTS measurements. It turns out that the typically 500  $\mu\text{m}$  diameter Al capacitors generally suffer from a rather high forward gate leakage current from the 1  $\mu\text{A}$  to the several 100  $\mu\text{A}$  range at –2 V, which affects the 1 MHz C-V characteristics in the accumulation region, as shown in Fig. 1. The tendency for leaky devices increased for the FGA or fired samples, suggesting a correlation with the damaging or degradation of the oxide by creating trapping centers. For reasons of sample-mounting in the DLTS holder, only large-diameter ( $\geq 400 \mu\text{m}$ ) dots could be handled. Whenever possible, capacitors with low gate current have been characterized by DLTS. Alternatively, a pulse bias  $V_P$  was chosen sufficiently into accumulation to fill the interface traps but avoiding a high gate current (e.g.  $> -1$  V in Fig. 1), which may result in electron injection and recombination and gives rise to negative, minority-carrier deep-level peaks.

DLTS has been performed using a Fourier-Transform-based digital system. Spectra have been obtained either from a frequency scan at room temperature or a temperature scan from 75 to 320 K, typically, whereby the capacitors are repetitively pulsed from a depletion bias ( $V_R$ ) into accumulation ( $V_P$ ), during a pulse time  $t_P$ . Further experimental details have been reported before.<sup>26,27</sup>

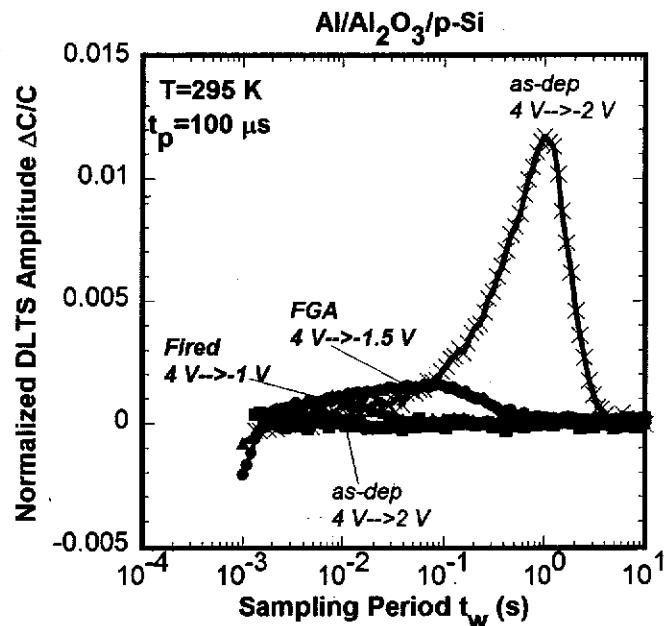

According to the isothermal DLTS-spectra of Fig. 2, a pronounced deep-level peak is observed in the as-deposited samples at room temperature. It is also clear that the associated traps occur at the  $\text{Al}_2\text{O}_3/\text{p-Si}$  interface since the spectrum recorded in depletion from 4 to 2 V, which only probes traps in the Si substrate, is essentially flat. After FGA or firing, the magnitude of the peak has drastically reduced, suggesting partial passivation of the underlying interface states by atomic hydrogen. At the same time, the peak maximum shifts to a lower sampling period  $t_w$ , indicating a lowering of the activation energy towards the valence band. Note that in Fig. 2 the DLTS amplitude has been divided by the steady-state capacitance in order to have a better quantitative comparison of the spectra for the different samples.

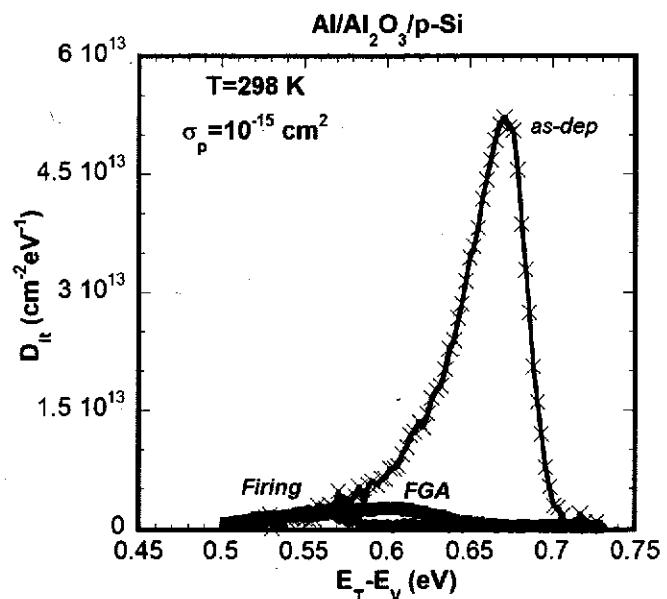

Since the spectra of Fig. 2 are associated with interface states, a  $D_{it}$  spectrum can be calculated, following the procedures outlined elsewhere.<sup>26,27</sup> The result is displayed in Fig. 3, confirming the conclusion derived from Fig. 2, namely, that FGA and firing lowers the  $D_{it}$  at the  $\text{Al}_2\text{O}_3/\text{p-Si}$  interface and at the same time moves the distribution towards lower activation energies. In the calculation of the

\* Electrochemical Society Active Member.

E-mail: eddy.simoen@imec.be

Figure 1. Capacitance-Voltage at 1 MHz (a) and Current-Voltage (b) characteristics at room temperature for a 5 nm  $\text{Al}_2\text{O}_3$  MIS capacitor as-deposited (■); after FGA (◊) and after a firing step (▲).

activation energy, a constant hole capture cross section of  $10^{-15} \text{ cm}^2$  was taken, which corresponds with the energy-averaged value, that has been derived from the intercept of the Arrhenius plots obtained from small-pulse-height measurements as a function of temperature. The peak  $D_{it}$  values for the as-deposited  $\text{Al}_2\text{O}_3$  sample are rather high, but are on the same order of magnitude as was reported recently for plasma ALD and  $\text{O}_3$ -ALD, where C-V measurements revealed densities in the range  $\sim 10^{13} \text{ eV}^{-1} \text{ cm}^{-2}$ .<sup>28</sup> However, much lower values on the order of  $3 \times 10^{11} \text{ eV}^{-1} \text{ cm}^{-2}$  have been found for  $\text{H}_2\text{O}$ -ALD layers on p-Si.<sup>28</sup> In addition, a  $D_{it}$  below  $10^{11} \text{ eV}^{-1} \text{ cm}^{-2}$  was reported for as-deposited  $\text{H}_2\text{O}$ -ALD  $\text{Al}_2\text{O}_3$  layers from conductance measurements using a mercury probe.<sup>29</sup> This suggests that the Al-gate deposition may also be partly responsible for the "as-grown"  $D_{it}$ .<sup>30</sup> Previous reports demonstrated a significant lowering of the  $D_{it}$  by FGA at the  $\text{Al}_2\text{O}_3/\text{p-Si}$  interface.<sup>22,28</sup> At the same time, it is shown that a low  $D_{it}$  is also obtained after a firing step only, in perfect agreement with the observations of Benick et al. and confirming the stability of the surface passivation after solar cell processing.<sup>20</sup>

Figure 2. (Color online) Isothermal frequency scan at room temperature for  $\text{Al}_2\text{O}_3$  MOS capacitors on p-Si, corresponding with: as deposited layer [pulse 4 V  $\rightarrow$  -2 V (x) and 4 V  $\rightarrow$  -2 V (■)]; after FGA [4 V  $\rightarrow$  -1.5 V (●)] and after firing [4 V  $\rightarrow$  -1 V (▲)]. A fixed pulse duration of  $100 \mu\text{s}$  was used.

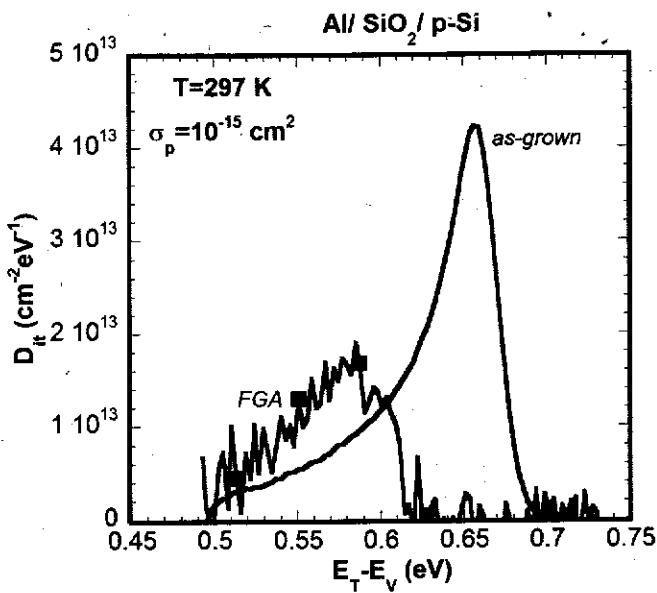

Comparing the  $D_{it}$  distribution of Fig. 3 for  $\text{Al}_2\text{O}_3$  capacitors with the 5 nm  $\text{SiO}_2$  reference samples in Fig. 4, one can conclude that rather similar results are obtained in both cases: a reduction of the  $D_{it}$  upon FGA and a shift towards lower activation energies. Note that according to the data of Figs. 3 and 4, FGA seems to be more effective in the case of  $\text{Al}_2\text{O}_3$ , which could be related to the presence of atomic H in the high-k layer coming from the  $\text{H}_2\text{O}$  precursor. Note that the peak  $D_{it}$  value for as-grown  $\text{SiO}_2$  is on the high side, compared with data obtained on 25 nm  $\text{SiO}_2$  layers on p-type Si.<sup>31</sup> Especially after FGA, the remaining  $D_{it}$  is still rather high

Figure 3. (Color online) Density of interface states versus energy with respect to the valence band maximum for an as-deposited  $\text{Al}_2\text{O}_3$  sample, after FGA and after a firing step. A hole capture cross section of  $10^{-15} \text{ cm}^2$  has been assumed.

Figure 4. (Color online)  $D_{it}$  distribution for 5 nm  $\text{SiO}_2$  MOS capacitors on p-type Si: as-grown and after FGA.

indicating that the hydrogen passivation is not so effective for the observed mid-gap interface states, in line with other recent observations.<sup>22,26,27</sup> Note finally that the FGA conditions chosen here are not optimal for interface state passivation but have been selected to yield the best recombination lifetime for our process conditions.

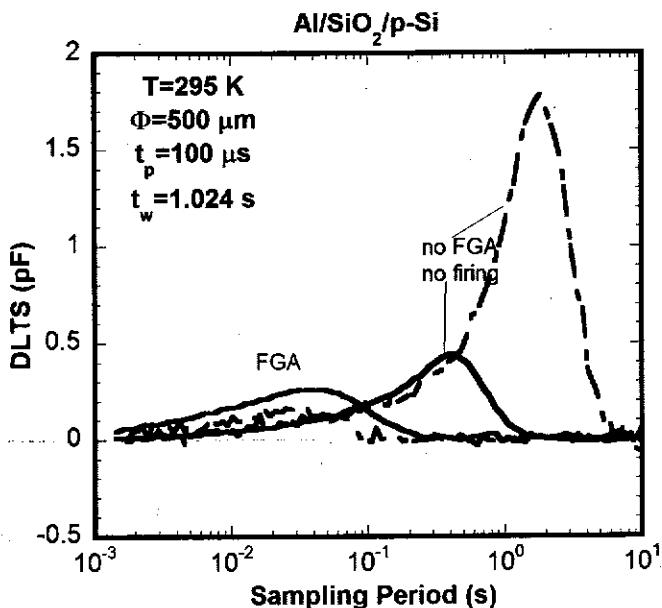

At the same time, one should be cautious in drawing too strong quantitative conclusions, as the DLTS and  $D_{it}$  spectra can exhibit quite some device to device scatter, as illustrated by Fig. 5. However, the similarity of both distributions in Figs. 3 and 4 strongly suggests that the same type of interface traps are being probed, namely associated with the Si/ $\text{SiO}_2$  interface. In the case of the  $\text{Al}_2\text{O}_3$  samples, the interface states are formed at the thin  $\text{SiO}_2$  interfacial layer. X-ray Photo-Electron (XPS) spectroscopy revealed no detectable  $\text{SiO}_2$  in the as-deposited samples, but after FGA and

Figure 5. (Color online) DLTS-spectra for two 5 nm  $\text{SiO}_2$  samples without post-metallization treatment (no FGA, no firing) and two samples after FGA, showing the sample-to-sample dispersion.

firing, a regrowth occurs, yielding a thickness of 0.26 and 1.51 nm, respectively. This is also confirmed by Electron Spin Resonance (ESR), showing the presence of  $\sim 10^{12} \text{ cm}^{-2}$  dangling bond centers, typical for the  $\text{SiO}_2/\text{Si}$  interface.

In summary, it has been shown by DLTS that the density of interface states is strongly reduced after post-Al-metallization FGA or firing of  $\text{Al}/\text{Al}_2\text{O}_3/\text{p-Si}$  MOS capacitors, while at the same time, the activation energy of the interface states shifts to lower values. Both factors should contribute to the improvement of the surface recombination properties of  $\text{Al}_2\text{O}_3$  passivated p-type Si.

### Acknowledgments

T. Conard and I. Vaesen are gratefully acknowledged for the XPS data. H. Vrielink and J. Lauwaert are kindly thanked for the use of the digital DLTS system at the University of Ghent.

### References

1. G. D. Wilk, R. M. Wallace, and J. M. Anthony, *J. Appl. Phys.*, **89**, 5243 (2001).

2. R. S. Johnson, G. Lucovsky, and I. Baumvol, *J. Vac. Sci. Technol. A*, **19**, 1353 (2001).

3. S. Jakschik, A. Avellan, U. Schroeder, and J. W. Bartha, *IEEE Trans. Electron Devices*, **51**, 2252 (2004).

4. O. Blank, H. Reisinger, R. Stengl, M. Gutsche, F. Wiest, V. Capodieci, J. Schulze, and I. Eisele, *J. Appl. Phys.*, **97**, 044107 (2005).

5. J. Buckley, B. De Salvo, D. Delenuyelle, M. Gely, G. Nicotra, S. Lombardo, J. F. Damlecourt, Ph. Hollinger, F. Martin, and S. Deleoni, *Microelectron Eng.*, **80**, 210 (2005).

6. I. Crupi, R. Degraeve, B. Govoreanu, D. P. Brunco, P. Roussel, and J. Van Houdt, *Microelectron Reliab.*, **47**, 525 (2007).

7. M. Cho, R. Degraeve, P. Roussel, M. B. Zahid, B. Govoreanu, B. Kaczer, E. Simoen, M. Jurczak, J. Van Houdt, and G. Groeseneken, *Solid-State Electron.*, **54**, 1384 (2010).

8. G. Agostinelli, A. Delabie, P. Vitanov, Z. Alexieva, H. F. W. Dekkers, S. De Wolf, and G. Beaucarne, *Solar Energy Mater. Sol. Cells*, **90**, 3438 (2006).

9. B. Hoex, J. Schmidt, R. Bock, P. P. Altermatt, M. C. M. van de Sanden, and W. M. M. Kessels, *Appl. Phys. Lett.*, **91**, 112107 (2007).

10. B. Hoex, J. Schmidt, P. Pohl, M. C. M. van de Sanden, and W. M. M. Kessels, *J. Appl. Phys.*, **104**, 044903 (2008).

11. G. Dingemans, P. Engelhart, R. Seguin, F. Einsele, B. Hoex, M. C. M. van de Sanden, and W. M. M. Kessels, *J. Appl. Phys.*, **106**, 114907 (2009).

12. W. C. Sun, W. L. Chang, C. H. Chen, C. H. Du, T. Y. Wang, T. Wang, and C. W. Lan, *Electrochem. Solid-State Lett.*, **12**, H388 (2009).

13. G. Dingemans, M. C. M. van de Sanden, and W. M. M. Kessels, *Electrochem. Solid-State Lett.*, **13**, H76 (2010).

14. P. Saint-Cast, D. Kania, M. Hofmann, J. Benick, J. Rentsch, and R. Preu, *Appl. Phys. Lett.*, **95**, 151502 (2009).

15. P. Saint-Cast, J. Benick, D. Kania, L. Weiss, M. Hofmann, J. Rentsch, R. Preu, and S. W. Glunz, *IEEE Electron Device Lett.*, **31**, 695 (2010).

16. R. Rao and F. Irrera, *J. Appl. Phys.*, **107**, 103708 (2010).

17. S. Miyajima, J. Irikawa, A. Yamada, and M. Konagai, *Appl. Phys. Express*, **3**, 012301 (2010).

18. J. J. H. Gielis, B. Hoex, M. C. M. van de Sanden, and W. M. M. Kessels, *J. Appl. Phys.*, **104**, 073701 (2008).

19. N. M. Terlinden, G. Dingemans, M. C. M. van de Sanden, and W. M. M. Kessels, *Appl. Phys. Lett.*, **96**, 112101 (2010).

20. J. Benick, A. Richter, M. Hermle, and S. W. Glunz, *Phys. Status Solidi (RRL)*, **3**, 233 (2009).

21. G. Dingemans, W. Beyer, M. C. M. van de Sanden, and W. M. M. Kessels, *Appl. Phys. Lett.*, **97**, 152106 (2010).

22. B. Imangholi, F. L. Lie, H. G. Parks, and A. J. Muscat, *IEEE Trans. Electron Devices*, **57**, 877 (2010).

23. F. Huster, in Proceedings of the 20th EU PVSEC, European Union, p. 1466 (2005).

24. A. Rothschild, B. Vermang, X. Loozen, B. J. O'Sullivan, J. John, and J. Poortmans, in Proceedings of the 25th EU PV Conference, p. 826 (2010).

25. I. S. Jeon, J. Park, D. Eom, C. S. Hwang, H. J. Kim, C. J. Park, H. Y. Cho, J.-H. Lee, N.-I. Lee, and H.-K. Kang, *Appl. Phys. Lett.*, **82**, 1066 (2003).

26. C. Gong, E. Simoen, N. Posthuma, E. Van Kerschaever, J. Poortmans, and R. Mertens, *Appl. Phys. Lett.*, **96**, 103507 (2010).

27. C. Gong, E. Simoen, N. E. Posthuma, E. Van Kerschaever, J. Poortmans, and R. Mertens, *J. Phys. D*, **43**, 485301 (2010).

28. G. Dingemans, N. M. Terlinden, D. Pierreux, H. B. Profijt, M. C. M. van de Sanden, and W. M. M. Kessels, *Electrochem. Solid-State Lett.*, **14**, H1 (2011).

29. J. M. Raffi, M. Zabala, O. Beldarrain, and F. Campabadal, *J. Electrochem. Soc.*, **158**, G108 (2011).

30. X. Loozen, B. J. O'Sullivan, A. Rothschild, B. Vermang, J. John, and I. Gordon, *Phys. Status Solidi (RRL)*, **4**, 362 (2010).

31. E. Simoen, C. Gong, N. E. Posthuma, E. Van Kerschaever, J. Poortmans, and R. Mertens, *J. Electrochem. Soc.*, **158**, H612 (2011).