### ALTERNATING SPACE-CHARGE-LIMITED CURRENTS IN HYDROGENATED AMORPHOUS SILICON

W. den Boer and A.F.P. Pop

Department of Electrical Engineering, Delft University of Technology, 2600 GA Delft, The Netherlands

(Received 22 October 1982 by M. Cardona)

Space-charge-limited currents in nt-i-nt sandwich samples of hydrogenated amorphous silicon have been investigated under alternating current (AC) conditions. When the voltage sweeping rate exceeds the release rate of carriers from deep traps, the AC current-voltage characteristics differ markedly from the direct current (DC) characteristics. This is attributed to the remaining space charge in the samples which acts as a potential barrier and reduces the current. A simple model is proposed to describe the time-dependence of this injection-induced barrier.

### 1. Introduction

In several recent papers the observation of space-charge-limited currents (SCLC) in hydrogenated amorphous silicon (a-Si:H) has been reported, either in forward biased Schottky diodes  $^{1,2}$  or in  $^{n+}$ -i- $^{n+}$  sandwich devices  $^{3,4}$ ,  $^{5}$  and in a lateral configuration  $^6$  . SCLC measurements provide information on the density and distribution of gap states<sup>7,8</sup>. Densities of states near midgap between 1016 and 1017 cm-3 eV-1 have been deduced from SCLC experiments on a-Si:H  $n^+-i-n^+$  devices  $3^{,4,5}$  .

In this paper we present current-voltage characteristics of n+-i-n+ devices at AC conditions and propose a model to explain the large discrepancy between AC and DC characteristics.

## 2. Experimental

The a-Si:H films have been produced by rf glow discharge decomposition of silane at a substrate temperature of 275 °C. For the n+ contact layers, which had a thickness of 50 nm, a mixture of 1% phosphine in silane was used. Glass plates with evaporated chromium stripes have been used as substrates. As upper electrodes chromium stripes were evaporated perpendicular to the lower electrodes, the overlapping area (1 or 4 mm<sup>2</sup>) defining the device.

Chromium-coated single-crystal silicon has also been used as a substrate. In this case chromium dots with an area of 0.5 or 10mm2 provided the upper contact.

# 3. The Model

A triangular sweep voltage with amplitude V is applied to the n+-i-n+ sandwich device in the SCLC regime. The injected charge is, in a first approximation, homogeneously distributed through the film and resides predominantly in deep traps  $^{\!3}$  . First,we consider the hypothetical situation that the release time of carriers from traps is infinite. Then the space charge per unit area in the sample is constant, Q:

$$Q_{o} = \frac{2\varepsilon_{s} V_{o}}{T}$$

(1)

where  $\epsilon_s$  is the semiconductor permittivity and L the undoped layer thickness.  $\textbf{Q}_o$  is related to the trap distribution  $N_{+}(E)$  by

$$Q_{o} \approx eL \int_{E_{Y_{O}}}^{E_{F_{1}}} N_{t}(E) dE$$

(2)

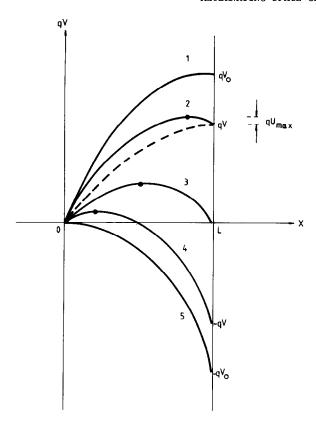

where  $\rm E_{Fo}$  and  $\rm E_{Fn\,l}$  are the equilibrium Fermi-level and the quasi-Fermi level at applied bias Vo respectively. The energy band profiles at different voltages can be deduced from Poisson's equation and are shown in figure 1. At a bias V with  $|V| < V_0$  a potential barrier  $U_{\rm max}$  is located

$$x_{\text{max}} = \frac{V_{\text{o}} + V}{2V_{\text{o}}} L \tag{3}$$

with

$$v_{\text{max}} = \frac{(v_o - |v|)^2}{4v_o}$$

(4)

In a practical device carriers are released from traps and  $\rm U_{\rm max}$  decreases with time. The realistic energy band profile lies between the dashed curve, which represents the steady-state profile at bias V, and curve 2 in figure 1. The traps are refilled again up to E  $_{Fn\,l}$  after application of the peak bias +V  $_{o}$  or -V  $_{o}$ . The release time  $\tau(E)$  of a trap located at

energy E is given by

(5)

where Ec is the energy level of the conduction band edge and the preexponential factor A is assumed constant. When the voltage is reduced from  $V_{\rm O}$  to V at a rate much faster than the release

Figure 1. Energy band profiles at different voltages and with constant space charge. The dashed line is the steady state profile at bias V.

rate of electrons from traps, the excess density of occupied traps N(E,t) is given by

$$N(E,t)=N_{t}(E)\exp\left(\frac{-t}{\tau(E)}\right)\left(\frac{1}{1+\exp\left(\frac{E-E}{kT}\right)}-\frac{1}{1+\exp\left(\frac{E-E}{kT}\right)}\right)$$

Here t is the time elapsed since the last peak bias has been applied and  $E_{\mbox{Fn}2}$  is the quasi-Fermi level at bias V.

When retrapping effects are neglected, the charge per unit area evolves in time as

$$Q(t) = \frac{2\varepsilon_s V}{T_s} + Q'(t)$$

(7)

with

(8)

$$Q'(t) = eL \int N(E,t)dE$$

The time dependence of  $\rm U_{max}$  is then obtained by replacing  $\rm V_{O}$  in equation (4) by

$$|V| + LQ'(t)/2\varepsilon_c$$

and given by

$$U_{\text{max}}(t) = \frac{\left( LQ'(t)/2\varepsilon_{s} \right)^{2}}{4\left( |V| + LQ'(t)/2\varepsilon_{s} \right)}$$

(9)

The AC current i at voltage  $\ensuremath{\mathsf{V}}$  is related to the barrier height by

$$i = C \exp\left(-\frac{eU_{max}(t)}{kT}\right) \tag{10}$$

Under the condition that the energy band profile is only slightly different from the steady-state profile, i.e.  $U_{\max}(t) << V$ , the constant C can, in a first approximation, be taken equal to i, the steady-state current at applied bias V. Then.

$$i = i_0 \exp \left(-\frac{eU_{max}(t)}{kT}\right)$$

(11)

The model predicts that the potential barrier decay time depends on  $\mathbf{E_c} - \mathbf{E_{FO}} = \mathbf{E_a}$ , the conductivity activation energy, for fixed  $\mathbf{N_t}(\mathbf{E})$ ,  $\mathbf{V_o}$ ,  $\mathbf{V}$  and  $\mathbf{L}$ , since for increasing  $\mathbf{E_a}$  the quasi-Fermi levels lie also deeper in the gap and hence the release time from traps between  $\mathbf{E_{Fn\,l}}$  and  $\mathbf{E_{Fn\,2}}$  increases.

## 4. Results and Discussion

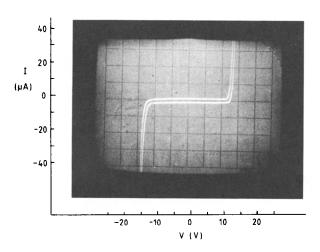

In figure 2 a current-voltage-oscillogram of a  $n^+$ -i- $n^+$  device is shown. The ramp voltage

Figure 2. Current-voltage oscillogram of a n<sup>+</sup>-1-n<sup>+</sup> device at a frequency of 500 Hz and an amplitude of 15 V.

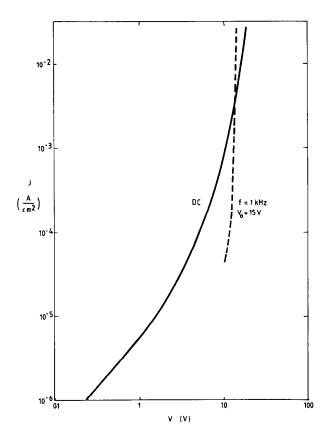

had a frequency of 500 Hz and an amplitude of 15 V. The area of the device was  $0.5~\text{mm}^2$  and the thickness L of the undoped layer 1.5~µm. The hysteresis in the high current region is due to the difference in elapsed time, defined in the previous section, for the curves with increasing and decreasing bias. In the low bias region the device acts as a capacitor and the hysteresis in this region is due to displacement currents. In figure 3 the comparison is shown between the DC characteristic and the AC characteristic at a frequency of 1 kHz and an amplitude of 15 V. In figure 4 the same data are plotted on a double-logarithmic scale. For the AC characteristic the transition to the high current regime is much sharper and occurs at a higher voltage. The voltage for onset of high current at

Figure 3. DC and AC characteristics on a linear scale for a device with L=1.5  $_{\mbox{\sc l}}$  m.

Figure 4. DC and AC characteristics on a double-logarithmic scale for a device with L=1.5  $\mu\,\text{m}$  .

fixed f=1kHz increases with increasing amplitude V<sub>O</sub>, from 4 V at V<sub>O</sub>= 5 V to 12 V at V<sub>O</sub>= 15 V, in accordance with the model.

With increasing voltage the AC characteristic approaches and crosses the DC characteristic. Beyond the crossing point the AC current exceeds the steady-state current. This can be attributed to transient currents which occur before the establishment of a new quasi-Fermi level. They are considerably larger than the steady-state current due to the progressive thermalization of trapped electrons. This thermalization process is also responsible for dispersive transport in disordered semiconductors of the progressive transport in disordered semiconductors.

The large variation of the current-voltage characteristics with frequency and amplitude is observed in many samples with different values of L and  $\rm E_a$ . The frequency at which deviations from the DC characteristic start, depends on  $\rm E_a$  as predicted by the model. Even on one sample  $\rm E_a$  can be modified by the Staebler-Wronski-effect  $^{10}$ .

We compared the characteristics of a sample in the light-soaked state ( $E_a$ =.61 eV) with those of the same sample in the annealed state ( $E_a$ =.51 eV). The current is restored to  $i_0$  on a time scale of minutes and seconds respectively, in qualitative agreement with the model.

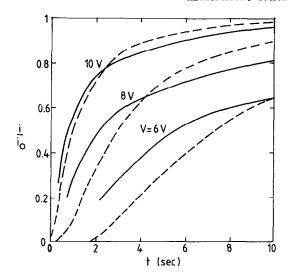

To check the consistency of the model more quantitatively we have measured the response of the current to a voltage step from V to V and compared the results with numerical calculations using equations (2), (5), (6), (8), (9) and (11). The ratio i/i\_0 is plotted in figure 5 as a function of elapsed time t for a device with L = 1.5  $\mu m$  and  $E_c-E_{FO}=0.7$  eV. The solid and dashed lines represent the measured and calculated results respectively for  $V_o=16$  V and V = 6,8 and 10 V. For the calculations the preexponential factor A in equation (5) was taken equal to  $10^{-11}$  sec?  $N_t(E)$  was determined from the DC current-voltage characteristic by the method described in our previous paper3 and was found to be equal to  $7.10^{16}~eV^{-1}\mbox{cm}^{-3}$ , independent of energy, in the range of interest between  $E_{FO}$  and  $E_{ED1}$ .

The shape of the measured curves and their dependence on V agrees well with the calculated results. However, slight modifications in the values of  $E_{FO}$ ,  $N_{t}(E)$  and temperature result in large changes of the time scale for the calculated curves, without changing their shape. Since  $E_{FO}$  and  $N_{t}(E)$  are not known with great accuracy (e.g. an error of a factor 2 is possible in  $N_{t}(E)^{3}$ ), the good quantitative agreement between calculated and measured results in figure 5 is not very significant.

In summary, we have shown that alternating space-charge-limited currents can be considerably smaller than the DC current at the same applied voltage. The experimental results are qualitatively explained by a model in which the AC current is reduced by a potential barrier which is due to the remaining space charge in the sample. The charge storage effects are indicative of deep traps with a density  $10^{16}-\ 10^{17}$  eV  $^{-1}$  cm  $^{-3}$  , in agreement with steady-state SCLC measurements.

Acknowledgements - The authors express their appreciation to J. van Turnhout, M. Kleefstra and

Figure 5. The response of the current on a voltage step from V<sub>o</sub> = 16 V to V = 6,8 or 10 V.

The solid and dashed lines represent the measured and calculated results, respectively.

M. Ondris for helpful discussions and to M.J. Geerts for technical assistance. One of us (WdB) was financially supported by the Foundation for Fundamental Research on Matter (FOM).

### References:

- S. Ashok, A. Lester and S.J. Fonash, IEEE El. Device Letters, EDL-1,200 (1980)

- M.K. Han, W.A. Anderson, Y. Onuma, P. Sung, R. Lahri and J. Coleman, IEEE El. Device Letters, Vol. EDL-2, 198 (1981)

- El. Device Letters, Vol. EDL-2, 198 (1981)

3. W. den Boer, J. de Physique 42-C4, 451 (1981)

- K.D. McKenzie, P.G. LeComber and W.E. Spear, Phil. Magazine B 46, 377 (1982)

- E. Bhattacharya, S. Guha, K.V. Krishna and D.R. Bapat, J. Appl. Phys. 53, 6285 (1982)

- S. Furukawa, T. Kagawa and N. Matsumoto, Solid State Comm. 44, 927 (1982)

- 7. M.A. Lampert and P. Mark, Current Injection in Solids, Academic Press, New York (1970)

- K.C. Kao and W. Hwang, Electrical Transport in Solids, Pergamon Press, Oxford (1981)

- T. Tiedje and A. Rose, Solid State Comm. 37, 49 (1980)

- D.L. Staebler and C.R. Wronski, J. Appl. Phys. 51, 3262 (1980)