## Integration of a silicon nanowire array into a photovoltaic device

Simon Perraud<sup>1,\*</sup>, Séverine Poncet<sup>1</sup>, Sébastien Noël<sup>1</sup>, Hakim Marko<sup>1,2</sup>, Emmanuelle Rouvière<sup>1</sup>, Philippe Thony<sup>3</sup>, and Régis Delsol<sup>3</sup>

<sup>1</sup>CEA, LITEN, Laboratoire des Composants pour la Récupération d'Energie, 17 rue des Martyrs, F-38054 Grenoble Cedex 9, France.

<sup>2</sup>Institut des Matériaux Jean Rouxel, Université de Nantes, CNRS, 2 rue de la Houssinière, BP 32229, F-44322 Nantes Cedex 3, France.

<sup>3</sup>CEA, LITEN, Laboratoire des Composants Solaires, INES-RDI, Savoie Technolac, 50 avenue du Lac Léman, F-73377 Le-Bourget-Du-Lac, France.

\*Corresponding author. E-mail: [simon.perraud@cea.fr](mailto:simon.perraud@cea.fr)

### ABSTRACT

Silicon nanowire arrays grown by chemical vapour deposition were successfully integrated into functional photovoltaic devices. A crucial planarization step, achieved by embedding the nanowires in a spin-on glass matrix and subsequent polishing of the front surface, allowed to deposit a continuous and uniform conductive film on top of the nanowire array, and thus to form a high-quality front electrical contact. The silicon nanowire array solar cells fabricated using this process exhibited a parasitic series resistance as low as  $5 \Omega \cdot \text{cm}^2$ , which is a clear improvement compared to the recent literature.

### INTRODUCTION

Using nanostructures is a promising route for third-generation photovoltaics [1]. In particular, silicon nanowires (SiNWs) grown by chemical vapour deposition (CVD) have been considered as building blocks for radial junction solar cells [2], which could enable energy conversion efficiencies comparable with conventional wafer-based solar cells, while reducing processing costs. Furthermore, quantum confinement effects in SiNWs could be employed for fabricating all-silicon multi-junction solar cells, with efficiencies exceeding the Shockley-Queisser limit for single-junction cells [3].

Promising results have been reported for SiNW array solar cells by Tsakalakos *et al.* [4,5] and Stelzner *et al.* [6]. However, the energy conversion efficiency obtained so far is about 0.1% [4-6], which is low compared to the typical performances of conventional wafer-based devices. One of the possible causes for such modest performances is the presence of a very high parasitic series resistance.

Here, we propose an approach for integrating CVD-grown SiNW arrays into solar cells with low parasitic series resistance.

### EXPERIMENT

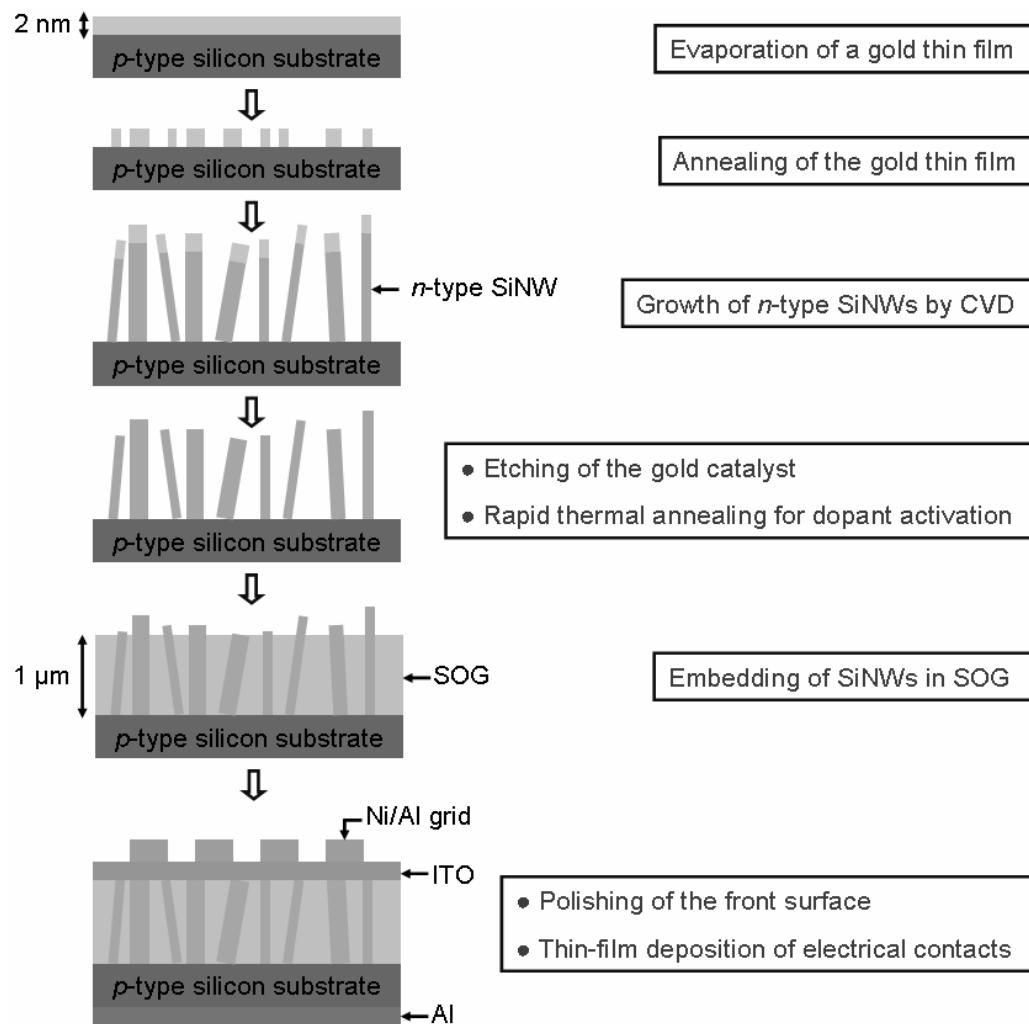

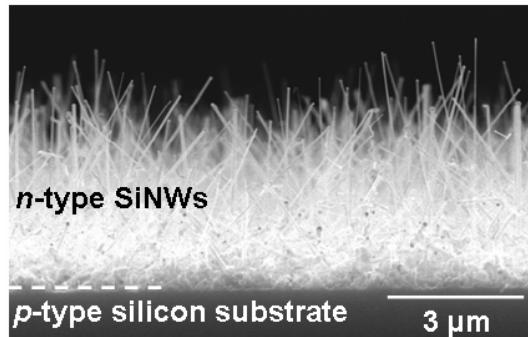

The process used in this work for integrating SiNW arrays into solar cells is presented in figures 1 and 2. We focus on a simple device structure, consisting of *n*-type SiNWs grown on a *p*-type silicon substrate. The *n*-type SiNWs were prepared by CVD via the gold-catalysed

vapour-liquid-solid method [7, 8], on (100)-oriented silicon substrates of *p*-type conductivity (14–22 Ω.cm). Silane (SiH<sub>4</sub>) and phosphine (PH<sub>3</sub>) were used as the silicon precursor and the phosphorous *n*-type dopant precursor, respectively. The PH<sub>3</sub>/ SiH<sub>4</sub> ratio was 2×10<sup>-3</sup>, corresponding to a nominal phosphorous concentration of 1×10<sup>20</sup> cm<sup>-3</sup>. Electrical resistance measurements of individual SiNWs, performed by scanning spreading resistance microscopy, were consistent with this nominal doping density.

**Figure 1.** Schematic presentation of the process for integrating SiNW arrays into photovoltaic devices.

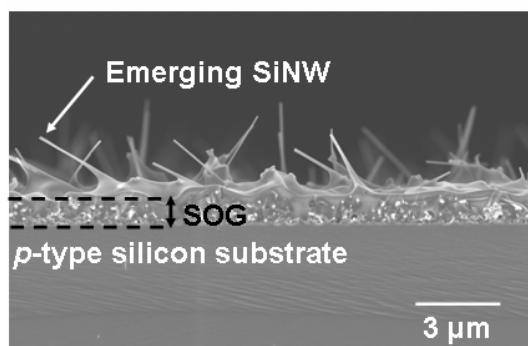

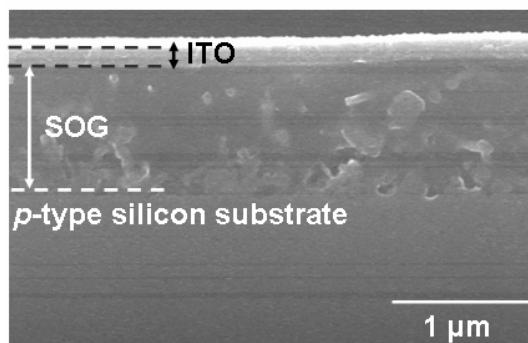

After the CVD growth of SiNWs, the gold catalyst was etched in a KI/I<sub>2</sub> solution, and the doping impurities were activated by rapid thermal annealing at 750°C for 5 min. The SiNWs were then embedded in a methylsiloxane SOG matrix, and the front surface was polished. An aluminium back electrical contact was deposited by sputtering, and annealed at 400°C in forming gas (4% of H<sub>2</sub> diluted in N<sub>2</sub>). An indium-tin oxide (ITO) front electrical contact was then deposited by sputtering on the planarized SOG surface. As shown in figure 2, this ITO layer is uniform and continuous. Finally, a Ni/Al front contact grid was deposited on top of the ITO electrode, by electron-beam evaporation through a mask.

Growth of *n*-type SiNWs by CVD

Embedding of SiNWs in SOG

- Polishing of the front surface

- Thin-film deposition of electrical contacts

**Figure 2.** Cross-section scanning electron microscopy images of a SiNW array at various steps of the process presented in figure 1.

The fabricated SiNW array solar cells were mounted using silver paint onto a copper-coated board. Devices were illuminated by halogen lamps, and current-voltage characteristics were recorded by using Kelvin probes. During measurements, device temperature was regulated at 25°C. The halogen lamp spectrum used for our experiments is slightly different from the standard AM1.5G spectrum. However, it was experimentally checked that for our SiNW array solar cells illuminated at 100 mW/cm<sup>2</sup>, the relative difference in energy conversion efficiency between the halogen lamp spectrum and the AM1.5G spectrum is less than 10%.

## RESULTS AND DISCUSSION

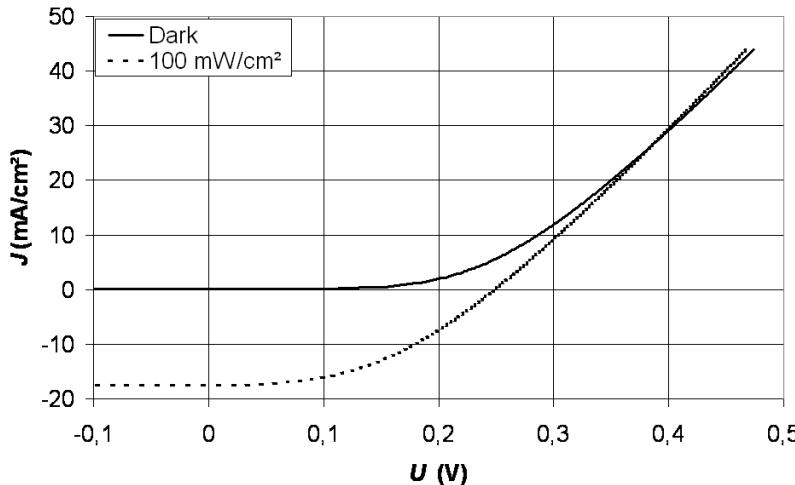

Figure 3 shows the dark and light current-voltage characteristics of a SiNW array solar cell, fabricated following the process presented in figure 1. The device active area is of the order of  $1 \text{ cm}^2$ . A clear rectifying effect is observed in the dark, with power generation under illumination. For an illumination intensity of  $100 \text{ mW/cm}^2$ , the short-circuit current is  $17 \text{ mA/cm}^2$ , the open-circuit voltage is  $250 \text{ mV}$ , the fill factor is  $44\%$ , leading to an energy conversion efficiency of  $1.9\%$ . The solar cell behaviour is ascribed to the  $pn$  junction formed between the  $n$ -type SiNWs and the  $p$ -type silicon substrate. It was checked that devices consisting of  $p$ -type SiNWs grown on  $p$ -type silicon substrates do not exhibit a rectifying effect.

The current-voltage characteristics shown in figure 3 become linear for  $U > +300 \text{ mV}$ , the slope corresponding to the parasitic series resistance  $R_S$ . It is found that  $R_S \approx 5 \Omega \cdot \text{cm}^2$ . This value is slightly larger than that of typical industrial silicon wafer solar cells ( $R_S \approx 2 \Omega \cdot \text{cm}^2$ ), but much lower than that of CVD-grown SiNW array solar cells reported in the recent literature: Tsakalakos *et al.* obtained an  $R_S$  value of several  $10 \Omega \cdot \text{cm}^2$  as it can be seen in figure 1 of Ref. [5], and Stelzner *et al.* obtained an  $R_S$  value of the order of  $150 \Omega \cdot \text{cm}^2$  as it can be seen in figure 3(a) of Ref. [6]. This important reduction of the parasitic series resistance is probably due to the fact that our process includes a planarization step of the SiNW array, allowing to deposit a continuous and uniform conductive layer on top of the SiNWs.

We performed measurements of the sheet resistance  $R_{sh}$  of the ITO thin film and of the specific contact resistance  $\rho_C$  between the ITO and the Ni/Al front contact grid, by employing the transmission line method. We found  $R_{sh} \approx 30 \Omega/\square$  and  $\rho_C \approx 3 \times 10^{-3} \Omega \cdot \text{cm}^2$ . Using these values, the contribution of the front electrical contact to the parasitic series resistance of our SiNW array solar cell was calculated to be about  $1.5 \Omega \cdot \text{cm}^2$ . The difference with the experimental value  $R_S \approx 5 \Omega \cdot \text{cm}^2$  cannot be explained by the SiNW array resistance (estimated to be of the order of  $10^{-4} \Omega \cdot \text{cm}^2$ ), but can be ascribed to the contact resistance between the SiNWs and the ITO layer.

**Figure 3.** Dark and light current-voltage characteristics of a SiNW array solar cell, fabricated following the process presented in figure 1. For an illumination intensity of  $100 \text{ mW/cm}^2$ , the short-circuit current is  $17 \text{ mA/cm}^2$ , the open-circuit voltage is  $250 \text{ mV}$ , the fill factor is  $44\%$ , leading to an energy conversion efficiency of  $1.9\%$ . The  $J$ - $U$  characteristics become linear for  $U > +300 \text{ mV}$ , the slope corresponding to the parasitic series resistance  $R_S$ . It is found that  $R_S \approx 5 \Omega \cdot \text{cm}^2$ .

## CONCLUSIONS

A novel process was developed for integrating CVD-grown SiNW arrays into functional photovoltaic devices. A crucial planarization step, achieved by embedding the SiNWs in a SOG matrix and subsequent polishing of the front surface, allowed to deposit a continuous and uniform ITO layer on top of the SiNW array, and thus to form a high-quality front electrical contact. The SiNW array solar cells fabricated using this process exhibited a parasitic series resistance as low as  $5 \Omega \cdot \text{cm}^2$ , which is a clear improvement compared to the recent literature. Future works for obtaining even lower series resistance will focus on improving the contact resistance between the SiNWs and the ITO layer.

## ACKNOWLEDGMENTS

We thank Joël Dufourcq, Caroline Celle and Jean-Pierre Simonato for useful discussions. This work was funded by the Agence Nationale de la Recherche (Carnot project “SUNPEAC”).

## REFERENCES

- [1] L. Tsakalakos, *Mater. Sci. Eng. R* **62**, 175 (2008).

- [2] B. M. Kayes, H. A. Atwater, and N. S. Lewis, *J. Appl. Phys.* **97**, 114302 (2005).

- [3] G. Conibeer, M. Green, E.-C. Cho, D. König, Y.-H. Cho, T. Fangsuwannarak, G. Scardera, E. Pink, Y. Huang, T. Puzzer, S. Huang, D. Song, C. Flynn, S. Park, X. Hao, and D. Mansfield, *Thin Solid Films* **516**, 6748 (2008).

- [4] L. Tsakalakos, J. Balch, J. Fronheiser, B. A. Korevaar, O. Sulima, and J. Rand, *Appl. Phys. Lett.* **91**, 233117 (2007).

- [5] L. Tsakalakos, J. Balch, J. Fronheiser, B. A. Korevaar, O. Sulima, and J. Rand, *SPIE Newsroom*, doi: 10.1117/2.1200804.1124 (2008).

- [6] Th. Stelzner, M. Pietsch, G. Andrä, F. Falk, E. Ose, and S. Christiansen, *Nanotechnology* **19**, 295203 (2008).

- [7] R. S. Wagner and W. C. Ellis, *Appl. Phys. Lett.* **4**, 89 (1964).

- [8] L. Latu-Romain, C. Mouchet, C. Cayron, E. Rouviere, and J.-P. Simonato, *J. Nanopart. Res.* **10**, 1287 (2008).