# “联合技术”测量界面态分布的 几个问题的分析

沈桂芬

(物理系)

## 摘要

本文以实验事实为依据详细地分析了用“联合技术”测量界面态密度可能产生误差的几种因素，例如归一化值的线性度偏差、扫描速率大小的选择、地电势的偏差等，提出了避免误差、提高测量精度的方法，还讨论了磷处理工艺、合金工艺及光照等对界面态密度的影响。

准静态—高频 C—V 联合技术测量界面态在禁带中的分布是一种简单易行的技术，它具有设备简单、数据处理容易等优点。测量范围在禁带中央约  $0.6 \text{ eV}$  左右，精度可达  $10^{10} \text{ eV}^{-1} \text{ cm}^{-2}$  [1]。关于用“联合技术”测量界面态的原理与方法已在前文 [2] 中做过详细阐述，下面仅就联合测量中影响测量精度的几个问题进行分析和通过对比实验得出影响界面态密度的工艺因素进行讨论。

## 一、在联合测量中造成界面态密度的误差的分析

1、归一化值的线性度偏差：在联合测量中常采用归一化测量，这样避免了由仪器本身精度不高所带来的误差，但归一化测量必须保证在输出端  $y$  笔 0~1.0 范围内属于测量仪器的线性区。现有仪器怎样才能保证归一化值的线性度呢？有两方面因素必须考虑：

(1) 扫描速率的偏差造成界面态密度  $N_{ss}$  的误差。

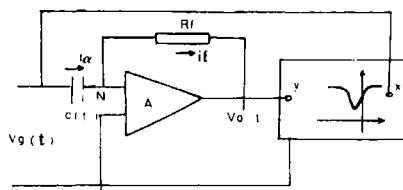

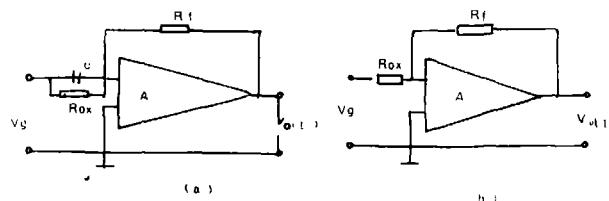

在联合测量中包括高频 C—V 和准静态 C—V 两部分测量，准静态部分测量原理如图 1 所示。

其中  $C(t)$  是待测 MOS 电容器样品， $R_f$  是反馈电阻， $A$  是高增益、高输入阻抗的运算放大器。

图 1 准静态测量原理图

1986 年 11 月 27 日收到

器。由 N 点“虚地”概念有：

$$i_f = -i_a = C(t) \frac{dV_g(t)}{dt}$$

输出电压为

$$V_o(t) = -i_f R_f = -R_f C(t) \frac{dV_g(t)}{dt} \quad \dots \dots \dots (1)$$

其中  $V_g(t)$  为一线性斜波电压，且

$$V_g(t) = V_1 + \alpha t$$

$$\therefore \frac{dV_g(t)}{dt} = \alpha \quad \dots \dots \dots (2)$$

$\alpha$  是扫描速率。

将 (2) 式代入 (1) 式中便有

$$V_o(t) = -\alpha R_f C(t) \quad \dots \dots \dots (3)$$

因此为保证运算放大器输出电压  $V_o(t)$  与  $C(t)$  成线性关系则要求  $\alpha$  必须为常数。如果  $\alpha$  随  $t$  有一微小变化则将直接影响  $V_o(t)$  值。

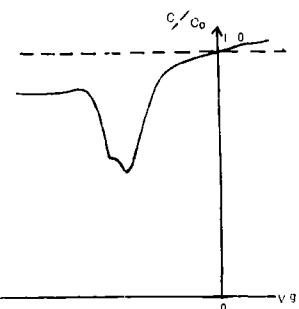

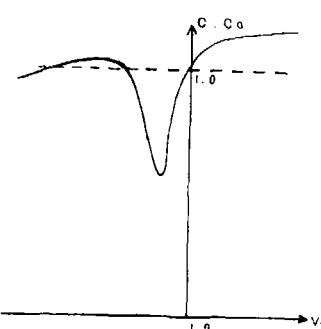

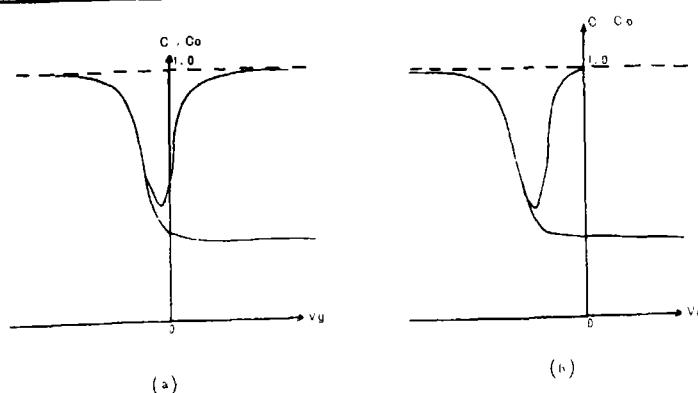

若  $\Delta\alpha < 0$ ，则输出电压值便由 1 下降，致使准静态  $C-V$  曲线在强反型以后仍回不到 1，在整个扫描过程中  $C_L(V_g)$  值均偏离真实值。同样，如果  $\Delta\alpha > 0$  则出现输出电压增大，超过 1，即所谓的过冲现象。图 2 给出  $\Delta\alpha \neq 0$  的两种情况下的  $C-V$

曲线。从图 2 中 a、b 均可明显看出  $\alpha$  的偏差对输出特性的影响。

(a).  $\Delta\alpha < 0$

(b).  $\Delta\alpha > 0$

图 2  $\Delta\alpha \neq 0$  情况下输出曲线

由于准静态  $C-V$  输出特性的改变，则直接影响界面态密度  $N_{SS}$  值。例如： $\Delta\alpha > 0$  则由曲线 a 读出的  $C_L(V_g)/C_{ox}$  值小于真实值，而由界面态密度表达式

$$N_{SS}(E) = \frac{\epsilon_{ox} \epsilon_0}{d_0 q^2} \left[ \frac{C_L(V_g)/C_{ox}}{1 - C_L(V_g)/C_{ox}} - \frac{C_{理}(V_g)/C_{ox}}{1 - C_{理}(V_g)/C_{ox}} \right] \quad [2]$$

$$\dots \dots \dots (4)$$

较小的  $C_L(V_g)/C_{ox}$  值计算出的  $N_{SS}(E)$  值将普遍变小，故使  $N_{SS}(E)$  测量值出现误差，即  $\Delta N_{SS}(E) < 0$ 。反之若  $\Delta\alpha > 0$ ，则由曲线 b 读出的  $C_L(V_g)/C_{ox}$  值普遍高于真实值，则由公式 (4) 所计算结果必然偏大。(实际上如图 2、b 所示曲线运用文献[1]给出的数据处理方法根本无法计算)

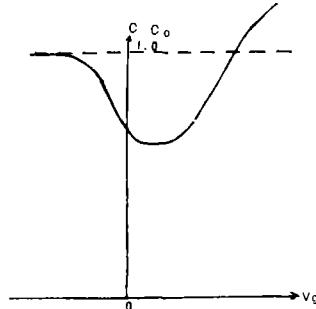

为避免上述由  $\Delta\alpha$  的存在造成  $N_{SS}$  的误差的出现，要在仪器选择和调整上下功夫。一般运算放大器当输入端用一固定电容器代替 MOS 样品时，测出归一化准静态  $C-V$  应基本上保持水平线，如图 3 所示，否则必然给  $N_{SS}(E)$  的计算带来误差。

(2) 样品漏电对  $N_{ss}$  的影响.

实际测量表明氧化层质量对测量有很大影响. 不计入  $\text{SiO}_2$  的漏电时准静态测量之等效电路如图 1 所示.

计入  $\text{SiO}_2$  的漏电后准静态测量的等效电路如图 4 中 (a) 所示. 即相当于在  $C(t)$  上并联了一个电阻  $R_{ox}$ .

为简单起见, 仅考虑  $R_{ox}$  的作用 (氧化层电阻  $R_{ox}$ ). 此时等效电路如图 4 中 b 所示.

在外加偏压下输出电压  $V_o(t)$

一方面随电容信号变化, 另一方面又迭加上了一个直流信号. 因此在负偏压端  $V_o(t)$  低于正常值, 而在正偏压端  $V_o(t)$  高于正常值, 所以当偏压从正到负 ( $n$  型衬底) 进行扫描时, 输出的准静态

$C-V$  曲线发生整体倾斜, 如图 5 所示. 显然这样的  $C/V_g$  曲线是无法利用文献[2]的方法进行数据处理的, 无法计算出界面态密度  $N_{ss}$  ( $E$ ) 的.

然而, 氧化层完全无漏电是不可能的. 从理论上分析, 氧化层漏电最大值为多少时才能运用文献[2]的方法计算界面态密度呢? 可采用如下方法大致估计一下  $\text{SiO}_2$  漏电的极限值.

如果扫描电压 = 8 V, 要求由漏电引起电压偏移小于百分之一, 即

$$\frac{\frac{1}{2}|\Delta V_0|}{|V_0|} \leq 1\% \quad (5)$$

(5) 式中  $\frac{1}{2}|\Delta V_0|$  表示在最大偏压下输出的偏移值,  $|V_0|$  表示无漏电时最大输出值.

由运算放大器原理可知

$$|V_0| = \alpha R_f C_{ox} \quad (6)$$

$$\frac{1}{2}|\Delta V_0| = |\frac{R_f}{R_{ox}} V_g| \quad (7)$$

$$\therefore \frac{\frac{1}{2}|\Delta V_0|}{|V_0|} = \left| \frac{V_g}{\alpha R_{ox} C_{ox}} \right| \quad (8)$$

(8) 式表示最大相对偏移值. 由 (8) 式解出  $R_{ox}$ :

$$R_{ox} = \left| \frac{V_g}{\alpha C_{ox} \frac{\frac{1}{2}|\Delta V_0|}{|V_0|}} \right| \quad (9)$$

图 3 用固定电容代替 MOS 样品时所测得的  $C-V$  曲线.

图 4 计入  $\text{SiO}_2$  漏电时的等效电路

图 5  $\text{SiO}_2$  漏电引起  $C-V$  曲线倾斜.

$$\text{取 } \frac{\frac{1}{2} |\Delta V_0|}{|V_0|} = 1\%, \quad |V_g| = 8 \text{ V}, \alpha = 300 \text{ mV/S},$$

$C_{OX} = 180 \text{ PF}$ , 代入(9)式中求出漏电阻最小值

$$R_{OX} = 1.48 \times 10^{13} \Omega.$$

漏电流最大值为

$$i_{OX} = \frac{|V_g|}{R_{OX}} = \frac{8}{1.48 \times 10^{13}} = 5.4 \times 10^{-13} \text{ A}.$$

所以在上述给定条件下 MOS 样品漏电应不大于  $5.4 \times 10^{-13} \text{ A}$ .

由漏电公式可知, 对漏电要求与选用样品的电容  $C_{OX}$  有关, 与扫描速率  $\alpha$  有关. 一般想放宽对漏电要求可选  $C_{OX}$  大的样品,  $\alpha$  可适当减少. 因此对一般的测试样品漏电应不大于  $10^{-13} \text{ A}$  数量级. 只有这样才能保证准静态输出曲线的正常, 才能保证界面态密度  $N_{SS}$  (E) 计算的精度.

## 2、扫描速率大小的选择造成 $N_{SS}$ 的误差:

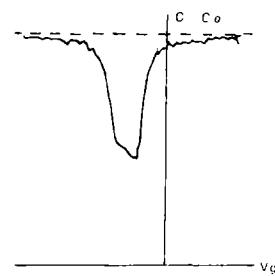

由于联合测量方法是利用在准静态条件下界面态电容的变化能跟得上信号的变化而体现出电容效应. 即信号变化的速率应使界面态来得及响应. 从这种意义上讲, 为使系统处于准静态则要求扫描速率  $\alpha$  越低越好. 但实验发现过底的扫描速率将使曲线变得不光滑, 如图 6 所示. 这是因为扫描速率过低致使噪声作用体现出来的结果. 显而易见, 这样的曲线是无法用于计算的.

$\alpha$  增大以后可使曲线变得光滑, 但过大的  $\alpha$  可使系统偏离准静态. 这时由于  $\alpha$  过大, 界面态电荷的变化跟不上信号的变化, 从而使输出值  $V_0(t)$  改变. 在积累区和耗尽区  $C_L / C_{OX}$  值将高于真实值, 在反型和强反型后  $C_L / C_{OX}$  将低于真实值. 所以由公式(4)计算出的  $N_{SS}$  值在积累、耗尽区偏高, 而在反型区则偏低.

多大的扫描速率才合适呢? 通过实验得知在满足漏电要求前提下, 一般将  $\alpha$  选在  $100 \text{ mV/S} \sim 300 \text{ mV/S}$  之间比较合适. 这样即消除了噪声干扰又满足准静态要求. 文章 [2] 中的几族曲线均是在这个范围内测得的.

## 3、地电势偏差的影响:

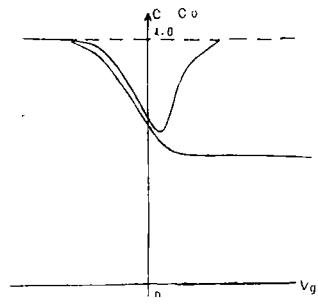

进行准静态测量时, 所用运算放大器(见图 1)输入端应严格保持“地电位”, 否则将给计算带来误差. 若 N 点对地电位  $V_N \neq 0$  则  $V_g = V_g - V_N$ . 若  $V_N < 0$ , 则  $V_g' > V_g$ , 则绘出的准静态曲线左移(如图 7 a), 这时高频  $C-V$  曲线在准静态  $C-V$  曲线上显然无法计算. 若  $V_N > 0$ ,  $V_g' < V_g$ , 这时准静态  $C-V$  曲线右移(见图 7 b), 使

图 6  $\alpha$  过低所引起的噪声的影响

图 7 地电势的偏差引起输出曲线的移动

之在积累区与高频 C - V 不重合。这种情况虽能计算，但误差较大。

为确保计算的准确性，一定要使 N 点对地电位为零，也就是要调整仪器在无信号输入时输出为零电位。

图 8 (a) 经磷处理样品的 C - V 曲线 (合金)

(b) 未经磷处理样品的 C - V 曲线 (合金)

## 二、从对比实验看磷处理工艺、合金工艺及光照等对界面态密度的影响

1、磷处理工艺：将同一批 MOS 样品，氧化后一部分经磷处理（生长磷硅玻璃）工艺，一部分不经磷处理工艺，分别制成样品，测试它们的 C - V 曲线分别在图 8 中(a)与(b)表示

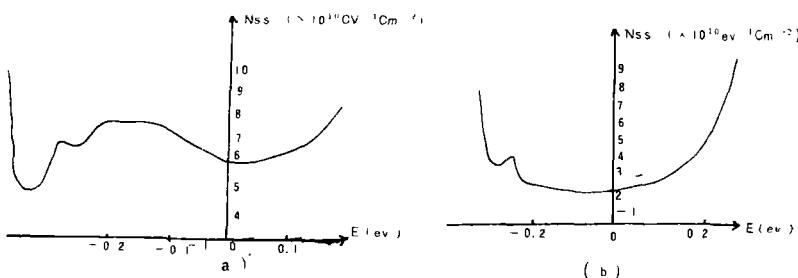

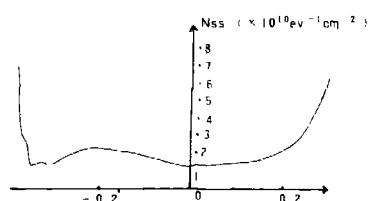

由此计算出  $V_g - V_s - E - N_{ss}$  (见表 I 与表 II)。图 9(a)与图 9(b)分别给出  $N_{ss} \sim E$  曲线。

表 I

|                                                     |       |       |       |       |       |      |       |       |       |      |      |      |      |       |       |

|-----------------------------------------------------|-------|-------|-------|-------|-------|------|-------|-------|-------|------|------|------|------|-------|-------|

| $V_g$ (V)                                           | -1.7  | -1.6  | -1.5  | -1.4  | -1.3  | -1.2 | -1.1  | -1.0  | -0.9  | -0.8 | -0.7 | -0.6 | -0.5 | -0.44 | -0.30 |

| $V_s$ (mV)                                          | -44   | -29   | -11   | 11    | 38    | 76   | 107   | 147   | 190   | 236  | 284  | 334  | 386  | 438   | 490   |

| $E$ (eV)                                            | -0.35 | -0.34 | -0.32 | -0.30 | -0.27 | 0.24 | -0.20 | -0.16 | -0.12 | 0.24 | 0.28 | 0.33 | 0.39 | 0.44  | 0.49  |

| $N_{ss}$ ( $\times 10^{10}$ eV $^{-1}$ cm $^{-2}$ ) | 9.63  | 5.17  | 4.81  | 5.04  | 6.74  | 6.52 | 7.64  | 7.54  | 7.52  | 6.78 | 6.07 | 5.91 | 6.22 | 6.82  | 8.16  |

表 II

|                                                     |       |       |       |       |       |       |       |       |       |       |      |      |      |      |

|-----------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|------|------|------|------|

| $V_g$ (V)                                           | -3.1  | -3.0  | -2.9  | -2.8  | -2.7  | -2.6  | -2.5  | -2.4  | -2.3  | -2.2  | -2.1 | -2.0 | -1.9 | -1.8 |

| $V_s$ (mV)                                          | 1     | 21    | 48    | 81    | 120   | 163   | 210   | 260   | 312   | 366   | 420  | 477  | 533  | 583  |

| $E$ (eV)                                            | -0.31 | -0.29 | -0.26 | -0.23 | -0.21 | -0.14 | -0.10 | -0.05 | 0.004 | 0.058 | 0.11 | 0.17 | 0.23 | 0.28 |

| $N_{ss}$ ( $\times 10^{10}$ eV $^{-1}$ cm $^{-2}$ ) | 7.50  | 3.83  | 3.31  | 4.01  | 2.52  | 1.95  | 1.88  | 1.92  | 2.05  | 2.25  | 2.72 | 3.73 | 5.58 | 9.66 |

经过比较和分析上述实验结果，看到未做磷处理样品在禁带中央界面态分布较平缓，且  $N_{SS} = 2 \times 10^{10} \text{ Cm}^{-2} \text{ eV}^{-1}$ 。而经磷处理工艺的样品界面态分布在禁带中央出现较大起伏，平均值为  $N_{SS} = 6 \times 10^{10} \text{ eV}^{-1} \text{ Cm}^{-2}$ 。经过

图 9 (a) 磷处理(合金)样品中计算出的  $N_{SS} \sim E$  关系曲线。

(b) 非磷处理(合金)样品中计算出的  $N_{SS} \sim E$  关系曲线。

对可动电荷测量表明经磷处理工艺可有效降低固定电荷密度，但对降低界面态密度效果不甚明显。

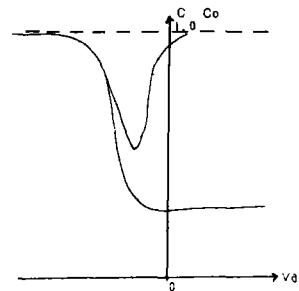

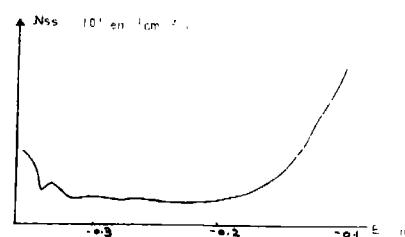

2、合金工艺的作用：反刻铝后不进行合金工艺，和进行合金工艺制成的 MOS 样品，测得的 C-V 曲线如图 10 与图 8(b)所示。计算  $V_g - V_s - E - N_{SS}$  关系列于表 III 与表 II 中。 $N_{SS} \sim E$  曲线见图 11 与图 9 (b)。

实验结果表明合金工艺的作用可使界面态密度降低一个数量级，其机理可用迪尔模型 [3] 进行解释。

迪尔模型认为  $\text{Si} - \text{SiO}_2$  界面过渡层的微观结构是由缺氧较多的不饱和键的  $\text{SiO}_2$  层形成，界面态是硅表面的缺陷和不饱和的 Si 键及氧的空位。合金时，氧透过  $\text{SiO}_2$  层达到界面，

图 10 反刻铝后不进行合金工艺的样品的 C-V 曲线

表 III

| $V_g$ (V)                                                 | -3.0   | -2.9   | -2.8   | -2.7   | -2.6   | -2.5   | -2.4  | -2.3  | -2.2  | -2.1  | -2.0  | -1.9  |

|-----------------------------------------------------------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|

| $V_s$ (mV)                                                | -66    | -60    | -52    | -43    | -32    | -8     | 8     | 28    | 51    | 78    | 108   | 141   |

| E (eV)                                                    | -0.384 | -0.378 | -0.370 | -0.361 | -0.350 | -0.326 | -0.31 | -0.29 | -0.27 | -0.24 | -0.21 | -0.18 |

| $N_{SS} (\times 10^{10} \text{ eV}^{-1} \text{ Cm}^{-2})$ | 6.60   | 3.43   | 2.51   | 2.12   | 0.90   | 1.07   | 0.99  | 1.23  | 1.65  | 1.92  | 2.00  | 2.01  |

| $V_g$ (V)                                                 | -1.8   | -1.7   | -1.6   | -1.5   | -1.4   | -1.3   | -1.2  | -1.1  | -1.0  | -0.9  | -0.8  | -0.7  |

| $V_s$ (mV)                                                | 177    | 217    | 260    | 306    | 353    | 400    | 448   | 493   | 536   | 572   | 602   | 625   |

| E (eV)                                                    | -0.14  | -0.1   | -0.06  | -0.012 | 0.035  | 0.081  | 0.13  | 0.175 | 0.218 | 0.254 | 0.284 | 0.31  |

| $N_{SS} (\times 10^{10} \text{ eV}^{-1} \text{ Cm}^{-2})$ | 1.79   | 1.58   | 1.34   | 1.22   | 1.29   | 1.34   | 1.47  | 1.76  | 2.31  | 3.30  | 4.42  | 6.66  |

填补了氧空位，从而使之减少，并使界面态密度明显下降。由实践证明合金工艺的作用不仅在于使 Al-Si 形成良好的接触，它还可以有效地降低界面态密度，这一点对 MOS 器件有重要意义。

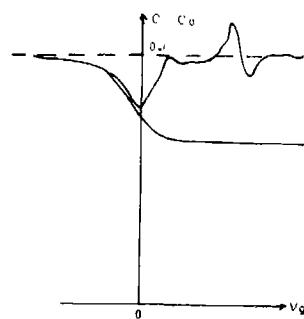

**3、光照的影响：**避光测量时 C-V 曲线明显光滑，可测范围较宽，在白炽灯照射下测出 C-V 曲线起伏较大，见图 12。这种曲线严格说是不能用于界面态密度计算的。C-V 曲线发生较大起伏是由于光照加快了界面态电荷的产生—复合作用，且这种产生—复合作用受光照的调制，从而大大地干扰了偏压对界面态电容的调制作用。这种 C-V 曲线显然无法计算  $N_{ss}$ 。即使将图 12 曲线作近似计算，也发现界面态可测范围变窄，界面态密度上升，如图 13 所示。

上述情况可解释为光照使得界面上的某些饱和键离化，从而增加了悬挂键的密度，故光照使界面态密度增加，测试范围变窄。可这样理解：光照使电子得到了附加能量，一些得到附加能量的电子足以脱离共价键束缚而激发到导带产生电子—空穴对。产生的电子—空穴对，在耗尽层两侧重新分布，使表面势减少，耗尽层厚度也减少，从而电容值增加，致使准静态 C-V 曲线上移，使  $C_L / C_{ox} \sim V_g$  与  $C / C_{ox} = 1.0$  所包围面积变小，所以能量 E 的范围变小，故导致界面态可测范围变窄。

图 12 光照下 C - V 曲线

图 11 不进行合金工艺样品的  $N_{ss} \sim E$  关系图 13 光照下样品的  $N_{ss} \sim E$  关系

能量，一些得到附加能量的电子足以脱离共价键束缚而激发到导带产生电子—空穴对。产生的电子—空穴对，在耗尽层两侧重新分布，使表面势减少，耗尽层厚度也减少，从而电容值增加，致使准静态 C-V 曲线上移，使  $C_L / C_{ox} \sim V_g$  与  $C / C_{ox} = 1.0$  所包围面积变小，所以能量 E 的范围变小，故导致界面态可测范围变窄。

### 三、结 论

#### 1、为提高联合技术测量界面态密度的精度，必须做到：

- (1) 扫描速率  $\alpha$  保持为常数。

- (2) 一般样品漏电不大于  $10^{-13} A$ 。

- (3) 扫描速率选取在  $100 mV / s \sim 300 mV / s$  之间。

- (4) 防止地电势的偏差。

#### 2、对比实验表明：

- (1) 磷处理工艺可有效降低  $SiO_2$  中可动电荷，但对降低界面态密度效果不明显。

- (2) 反刻铝后的合金工艺可有效降低界面态密度。

- (3) “联合技术”测量界面态密度的分布必须在避光无干扰情况下进行。

## 参 考 文 献

[ 1 ] M . kuhn . Solid State Eleetronic Vol. 13 ( 1970 ) No. 6.P873.

[ 2 ] 沈桂芬等.《辽宁大学学报》自然科学版第 1 期 ( 1986 )

[ 3 ] 郭威廉著《硅—二氧化硅界面物理》. 国防工业出版社, 北京, ( 1982 )

(责任编辑: 崔久满 彭学勤)

# The Analizing of Several Problem of Measurement of Distribution of interface State using “Joint Thechigue”

Shen Guifen

(Department of Physics, Liaoning University )

## ABSTRACT

The article is based on the experimental facts analizing carefully several factors the ability that can cause errors. For example. the deviation of linearity of normalizing value, the choice of scanning speed and earth potential deviation etc. It points out the methods of advoiding the errors and improving the precision of measurement. At last, through a lot of correlation experimental data, the effect of phosphorus processing, alloy technique; and illumination on the surface state toward density has been discussed.