文章编号:1003-8213(2008)05-0005-04

## 利用压印技术制备大面积相变材料阵列

刘彦伯<sup>1,2\*</sup>, 钮晓鸣<sup>1</sup>, 宋志棠<sup>2</sup>, 闵国全<sup>1</sup>, 万永中<sup>1</sup>, 张 静<sup>1</sup>, 周伟民<sup>1,2</sup>, 李小丽<sup>1</sup>, 张 挺<sup>2</sup>, 张剑平<sup>1</sup>

(1. 上海市纳米科技与产业发展促进中心 纳米加工技术实验室, 上海 200237;

2. 中国科学院上海微系统与信息技术研究所 纳米技术研究室, 上海 200050)

**摘要:**采用高效、低成本的紫外压印技术(UV-IL)在2 in. Si/SiO<sub>2</sub>基Ti/TiN/Si<sub>2</sub>Sb<sub>2</sub>Te<sub>3</sub>(SST)多层膜表面制备了密度为3.8 M/in<sup>2</sup>的AMONIL点阵结构,并通过反应离子刻蚀得到相变材料SST阵列;电阻与脉冲宽度特性测得SST基PCRAM存储单元SET/RESET电阻值变化约30倍,I-V特性表明,阈值电压为1.18 V。此外,时间分辨XRD原位加热情况下SST薄膜结构变化说明,SST材料的相变发生在200 ℃~300 ℃之间。

**关键词:**UV-IL; SST阵列; PCRAM; 存储单元

中图分类号:TN305 文献标识码:A

### 1 引言

围绕低压、低功耗、高速和高密度存储器件商业化进程,相变存储器(phase change random access memory, PCRAM)必须减小相变区域,提高集成密度,而相变材料(PCM)高密度阵列一致性制备是一个核心问题。当器件结构进入纳米尺度后,采用电子束曝光、聚焦离子束和光学曝光等常规微细加工技术的开发成本急剧增加,尤其是新材料和新结构为稳定性能要优化参数,致使开发成本更高,所以新材料筛选和新结构研究正面临高成本和低效率的困境。而紫外压印(UV imprint lithography, UV-IL)技术可以廉价地在大面积基片上重复、大批量的制备各种图形结构,具有精度高、效率高、成本低、尺寸一致性易于控制的综合优势<sup>[1-5]</sup>,正好满足新材料筛选和新结构加工研究需要,这将大大加速新相变材料和新存储结构的开发进程。目前这项技术的最高水平已达5 nm。Lee H等人研究了UV-IL制作Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>3</sub>网架结构<sup>[2]</sup>,Yang K-Y等人研究了UV-IL制作Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>3</sub>点阵结构<sup>[6]</sup>。而在新材料探索方面,Zhang T等人<sup>[7-8]</sup>的研究表明,Si<sub>2</sub>Sb<sub>2</sub>Te<sub>3</sub>(SST)比Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>3</sub>具有更好的数据保持力和稳定性、更宽的禁带宽度和更低的阈值电流;Zhang Y等人<sup>[9]</sup>报道,Si掺杂Sb<sub>2</sub>Te<sub>3</sub>薄膜比Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>3</sub>薄膜具有更低的融化温度和更高的晶态电阻。这些成果反映出SiSbTe材料体系在高密度存储领域的潜能优势。因此,本文利用UV-IL制备大面积新相变材料SST阵列,构筑PCRAM存储单元,为加速新相变材料

体系和PCRAM开发提供实验依据。

### 2 实验

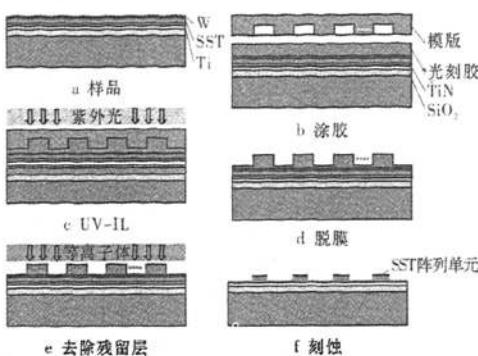

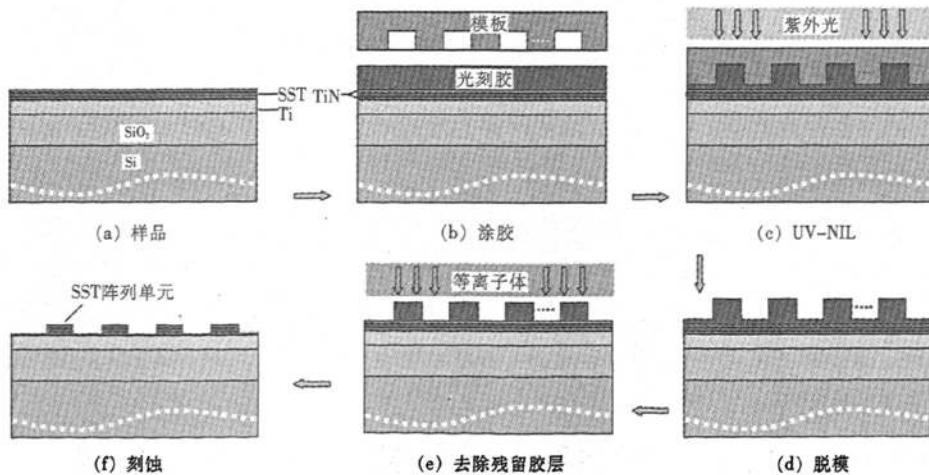

UV-IL制作相变材料SST阵列工艺流程如图1所示。首先在两块覆盖SiO<sub>2</sub>(经热氧化法生成)的硅片表面用溅射法分别沉积Ti, TiN和SST,厚度分别是100 nm, 40 nm和150 nm,SST薄膜用Si, Sb和Te单靶溅射,然后在其中一块上再沉积100 nm厚的W作UV-IL用(如图1a)。为防止脱模过程中模版和压印胶粘连,压印前用碳氟化合物对石英模版表面进行气相法处理45 min后150 ℃下退火1 h,在模版结构表面形成一层类似Teflon性质的自组装单分子膜,以减小表面能、降低其与压印胶之间的粘附力,处理过程是在氮气环境中进行的。接着在样品表面旋涂一层粘合剂和380 nm紫外压印胶AMONIL MMS4(AMO, GmbH, 德国),如图1b,涂覆粘合剂和压印胶后的样品分别置于电热板上100 ℃热烘1 min。最后,用2 in. 石英模版在EVG620(EV Group, 奥地利)上完成紫外压印工艺,压印力和曝光时间为70 kPa和300 s,如图1c和1d。压印后,用反应离子刻蚀(RIE)优化工艺首先去除残留胶,然后用不同工艺依次刻蚀W, SST和TiN层,如图1e和1f所示,实验在MS-350(ROTH & RAU, 德国)上进行。

加热过程中SST的结构变化规律和阵列单元特征尺寸以及PCRAM存储单元的电学特性分别通过XRD(X' Pert PRO MPD, Panalytical, 荷兰)和SEM(S-4800, Hitachi, 日本)以及脉冲信号发生器(Agilent 81104A)表征。

收稿日期:2008-07-22;修订日期:2008-08-20

基金项目:国家重大科学研究计划资助项目(2007CB935400);上海市科学技术委员会科研发展计划资助项目(0652nm052;0752nm013;0752nm014);上海市博士后重点科学基金资助项目(07R214204);中国博士后科学基金资助项目(20070420105)

作者简介:刘彦伯(1968-),男,陕西府谷人,副教授,博士,从事微纳加工技术及其在微电子器件中的应用研究。

\* 通讯作者

图 1 UV-IL 制作 PCM 阵列流程示意图

### 3 结果与讨论

#### 3.1 PCM SST 的相变性能

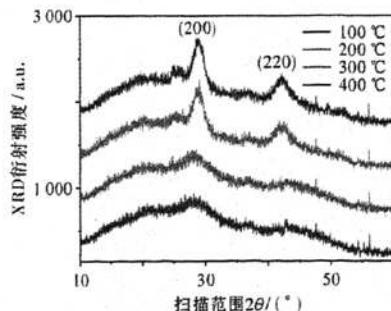

通过 XRD 检测 PCM SST 的相变过程和结构变化规律, 考证材料相变特性, 图 2 的材料结构变化结果说明, 在原位的 XRD 加热过程中, 非晶的 SST 材料在 200 °C 以下没有太大改变, 随着温度的上升, 材料出现明显的向多晶结构变化的趋势, 到了 300 °C 时, XRD 显示, 材料中逐渐出现多晶的晶粒, 说明材料在此时已经开始结晶, 并且随着温度的升高, 结晶状况继续改善。结果表明, SST 材料的相变发生在 200 °C ~ 300 °C 之间。

图 2 PCM SST 相变特性

#### 3.2 阵列加工

因为压印胶膜厚、成分均匀性和抗刻蚀性以及膜与基底

的黏附性直接影响 UV-IL 加工精度和后续工艺界面质量, 必须严格控制。实验用粘合剂层预处理样片表面的方法来增加亲水性, 同时筛选流动性以及刻蚀选择性好的紫外压印胶(AMONIL)来提高涂敷质量和加工性能。为避免粘合剂和压印胶涂层中残留气体影响压印效果, 采用热烘的方法将涂覆后的样片分置于电热板上热烘, 以促使溶剂充分挥发。

由于压印过程中模版结构与压印胶深度接触、挤压成型, 致使模版与压印胶分离(脱模)时黏附力很大, 极易发生粘连, 因此压印前降低精密石英模版的表面能, 以减小黏附力非常重要。

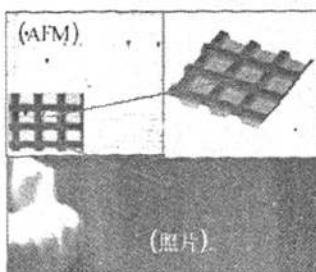

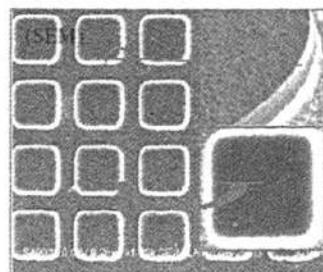

采用气相法处理后的孔阵列石英模版(见图 3)压印脱模时模版与压印胶完全分离, 且无剥离脱胶现象, 获得了结构清晰完整、单元尺寸均匀、边缘整洁平滑、残留层均匀的压印胶复型阵列, 如图 4 所示, 它是与模版凹凸对应的点阵列。结果表明, 气相法处理后形成的自组装单分子膜显著降低了石英模版表面能; 预处理工艺有效提高了光刻胶成膜均匀性及膜与基底的黏附性; 烘烤工艺解决了复型结构表面残留气孔问题。

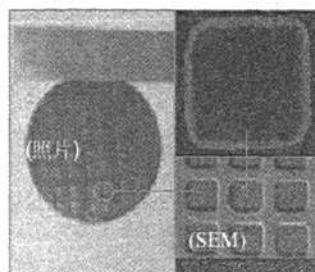

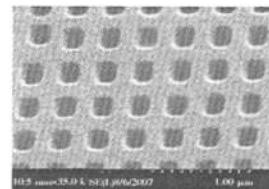

压印胶残留是压印光刻与传统光学光刻的一个显著区别, 能否完全去除残留胶对保证后续器件工艺和电学性能稳定尤为重要, 因此, 有效去除压印胶残留层是压印加工的一个关键问题。实验用含 O<sub>2</sub> 的混合等离子体完全去除了 AMONIL 残留层; 用含 CF<sub>4</sub> 的混合气体与功率的优化组合保证了后续刻蚀转移精度, 最终在 Ti/TiN 电极层上获得了单元结构均匀、完整的 SST 点阵如图 5 所示。

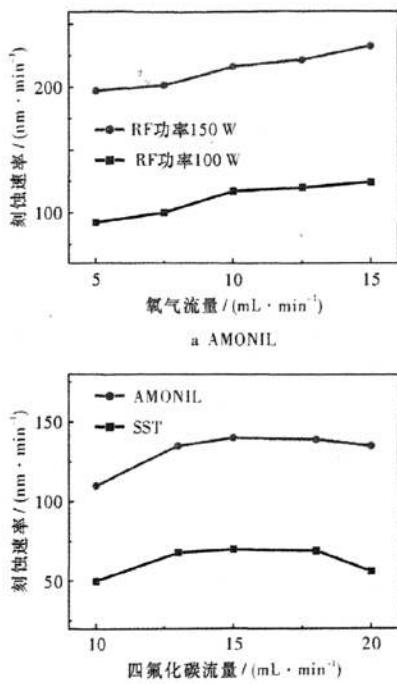

由于刻蚀过程中的薄膜损伤会严重影响器件性能及单元一致性, 因此刻蚀转移对薄膜低损伤要求很高, 通过优化刻蚀工艺, 既保证了图形转移精度, 又避免了薄膜损伤。图 6a 和 6b 分别是 O<sub>2</sub> 流量和射频功率对 AMONIL、CF<sub>4</sub> 流量对 SST 和 AMONIL 刻蚀速率的影响。

根据 AFM(图 2)和 SEM(图 3 和图 4)观察, 模版、AMONIL 和 SST 的阵列单元特征尺寸均值(25 个采样点)分别为 10.2 μm(S)、9.6 μm(R) 和 9.4 μm(E), 阵列密度 3.8 M/in<sup>2</sup>。并且, UV-IL 复型精度  $J_n$ ( $J_n = (1 - |R - S|/S) \times 100\%$ ) 为 94%, 误差源于模版处理和压印胶变形的影响; 刻蚀转移精度  $J_e$ ( $J_e = (1 - |E - R|/R) \times 100\%$ ) 为 97%, 误差源于刻蚀因子和高温形变等因素影响。这表明在考虑仪器和操作等误差因素的最不利影响情况下, SST 阵列单元的加工精度( $J = J_n \times J_e$ )超过 92%。若考虑误差叠加性则精度会更

图 3 模版阵列照片和 AFM

图 4 AMONIL 阵列照片和 SEM

图 5 SST 阵列 SEM

图 6 刻蚀工艺特性曲线

高些。结果显示,压印复型对加工精度影响较大,因此继续优化压印工艺有望进一步提高加工质量。

### 3.3 PCRAM 存储单元

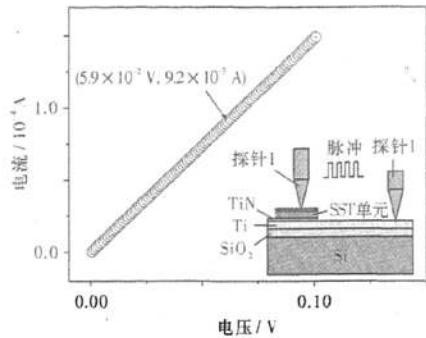

用 SST 阵列构筑 PCRAM 存储单元,并通过电学性能表征研究存储特性,图 7 中的插图是  $100 \mu\text{m}^2$  的 SST 存储单元结构示意图。为了检验各薄膜层成膜工艺及蚀刻质量,首先用数字信号进行了 I-V 测试,图 7 的结果表明,存储单元的 I-V 呈良好线性关系,说明各薄膜层之间是良好的欧姆接触,证明刻蚀转移过程中去胶均匀、完全,保证了良好的薄膜接触质量。

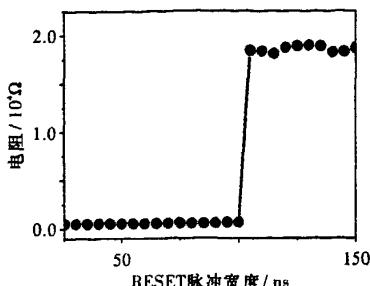

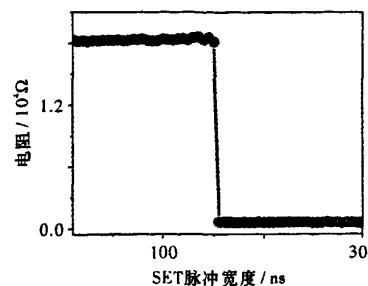

编程速率(擦写速率)是考证存储器性能优劣的一项重要指标,实验通过电阻与写脉宽( $R-T_{\text{RESET}}$ )特性予以表征,对所构筑的存储单元施加高度不变( $10 \text{ V}$ )、宽度逐渐增加的电压脉冲,并即时读取相应电阻,得到  $R-T_{\text{RESET}}$  特性曲线如图 8 所示,说明在施加脉冲高度不变的情况下,随着脉冲宽度的增加,上、下电极之间 PCM 区域积聚热能逐渐增加,当 PCM 区域温度升高到熔化温度之上,并且脉冲持续时间又不足以保证晶核生成时,实现了 PCM 从多晶到非晶的转变,完成了 RESET 过程。表现在  $R-T_{\text{RESET}}$  曲线上就出现了垂直分段现象,两种状态阻值变化达到 30 倍,并且分别稳定在  $18 \text{ k}\Omega$  和  $600 \Omega$  左右,说明存储单元具有比较稳定的非晶和多晶电阻值。而曲线中的突变点  $100 \text{ ns}$  就是存储单元从低阻到高阻状态转变的最佳脉冲宽度,这是影响编程速率的主要参数,是 PCRAM 存储单元结构、功耗和数据保持力等设计的必要参

图 7 I-V 测试(插图是 SST 存储单元结构示意)

数,因为存储器的编程速率、编程功耗和寿命之间密切相关。

同理,对存储单元施加高度固定、宽度逐渐增加的电压脉冲,并即时读取相应电阻,得到电阻与擦脉宽  $R-T_{\text{SET}}$  特性曲线。在  $6 \text{ V}$  的电压脉冲作用下,测试结果如图 9 所示,由  $R-T_{\text{SET}}$  曲线可见,当脉冲宽度超过  $155 \text{ ns}$  时,曲线出现了垂直突变,前后分为两段。这是因为脉冲高度一定,在脉宽较小的时候,由于加热时间太短,无法将上、下电极之间 PCM 加热到结晶温度以上,随着脉宽增加,PCM 区域积聚热能逐渐增加,当脉宽达到一定程度、积聚的能量足以加热 PCM 到结晶温度之上熔化温度之下,并且脉冲持续时间足以保证晶核生成时,PCM 实现了非晶到多晶的转化,存储单元就从高阻态突变为低阻态,完成了 SET 过程。表现在  $R-T_{\text{SET}}$  曲线上就出现了垂直分段现象,而曲线中的突变点  $155 \text{ ns}$  就是存储单元从高阻到低阻状态转变的最佳脉冲宽度,这是决定编程速率的主要参数,因为存储单元的擦(SET)写(RESET)特性是低压低功耗 PCRAM 设计的重要依据。

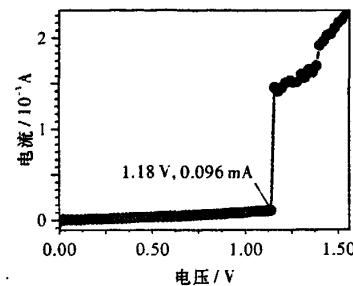

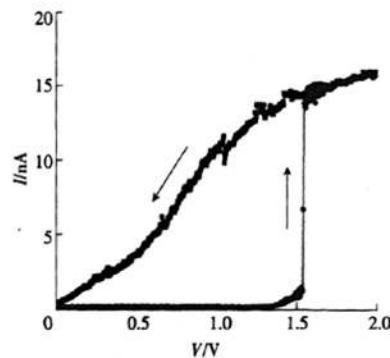

将该单元 SST 重新非晶化后,通过施加幅度逐渐增加的电压信号来测量存储单元对应的电流,进而分析其阈值电流( $I_{\text{th}}$ )和阈值电压( $V_{\text{th}}$ )。由于电压逐渐增加使得通过存储单元转化的热能相应增加,当聚集的热能使得 SST 单元温度升高到结晶温度之上熔化温度之下时,PCM SST 实现了从非晶到多晶的转变,引起了其电阻值的显著变化,反映在 I-V 特性曲线上则出现了不同斜率的两段曲线,如图 10 所示。由图可见,在持续稳定的电压信号达到  $1.18 \text{ V}$  后,两电极间电流突然从  $96 \mu\text{A}$  跳跃到  $1.5 \text{ mA}$ ,表明存储单元的  $I_{\text{th}}$  和  $V_{\text{th}}$  分别为  $96 \mu\text{A}$  和  $1.18 \text{ V}$ 。充分显示出 SST 在低功耗方面的潜能优势。

这里 SET 电压远大于 I-V 测试中的  $V_{\text{th}}$ ,其原因是因 I-V 测试中施加的是幅值按步长增加、持续  $200 \text{ ms}$  的连续信号;而  $R-T_{\text{SET}}$  操作中施加的是宽度逐渐增加的脉冲信号。因此,I-V 测试中电信号对 SST 单元是一个持续的加热过程,热累积效应促使其相变电压远远小于  $R-T_{\text{SET}}$  中的 SET 电压。

## 4 结论

本文针对 PCRAM 开发中迫切需要解决的大面积阵列制备关键问题,利用低成本、高效率的压印技术,探索性地开展

图 8 R-T<sub>RESET</sub> 特性曲线(10 V)图 9 R-T<sub>SET</sub> 特性曲线(6 V)

图 10 I-V 特性

了新型相变材料体系构建新结构存储单元阵列的关键技术研究，在 2 in. Si 基 TiN/Ti 电极层上制备了  $3.8 \text{ M}/\text{In}^2$  PCM SST 阵列，并检验了 SST-PCRAM 存储单元的电阻记忆功能，为 SST-PCRAM 设计开发提供了实验依据。结果表明，这是加快新材料新器件结构开发和性能研究进程的一条有效途径。而且，继续优化压印和刻蚀工艺参数将进一步提高阵列密度及一致性、稳定性，改变结构和测试方法将进一步加速纳米尺度新型材料、结构器件研发进程。

#### 参考文献：

- [1] Chou S Y, Kelmel C. Ultrafast and direct imprint of nano-structures in silicon [J]. Nature, 2002, 417 (20): 835 – 838.

- [2] Lee H , Hong S H , Yang K Y , et al . Fabrication of  $\text{Ge}_2\text{Sb}_2\text{Te}_3$  based PRAM device at 60 nm scale by using UV nanoimprint lithography [J]. Microelectronic Engineering, 2007, 84:573 – 576.

- [3] Chou S Y, Krauss P R, Renstrom P J. Imprint lithography with 25-nanometer resolution [J]. Science, 1996, 272:85 – 87.

- [4] Ito T, Okazaki S. Pushing the limits of lithography [J]. Science, 2000, 406:1027 – 1031.

- [5] Lee J J, Choi K B, Kim C H, et al. The UV-nanoimprint lithography equipment with multi-head imprinting unit for sub-50 nm half-pitch patterns [J]. Microelectronic Engineering, 2007, (84):963 – 966.

- [6] Yang K Y, Hong S H, Kim D K, et al. Patterning of  $\text{Ge}_2\text{Sb}_2\text{Te}_3$  phase change material using UV nano-imprint lithography [J]. Microelectronic Engineering, 2007, 84:21 – 24.

- [7] Zhang T, Song Z T, Rao F, et al. High speed chalco-genide random access memory based on  $\text{Si}_2\text{Sb}_2\text{Te}_5$  [J]. Jpn J Appl Phys, 2007, 46(11): L247 – 249.

- [8] Zhang T, Cheng Y, Song Z T, et al. Comparison of the crystallization of Ge-Sb-Te and Si-Sb-Te in a constant-temperature annealing process [J]. Scripta Materialia, 2008, 58:977 – 980.

- [9] Zhang Y, Feng J, Zhang Z F, et al. Characteristics of Si-doped  $\text{Sb}_2\text{Te}_3$  thin films for phase-change random access memory [J]. Appl Surf Sci, 2008, 264(10):1016 – 1020.

#### Fabrication of Phase Change Materials Large Area Array by Using UV Imprint Lithography

LIU Yan-bo<sup>1,2</sup>, NIU Xiao-ming<sup>1</sup>, SONG Zhi-tang<sup>2</sup>, MIN Guo-quan<sup>1</sup>, WAN Yong-zhong<sup>1</sup>,

ZHANG Jing<sup>1</sup>, ZHOU Wei-min<sup>1,2</sup>, LI Xiao-li<sup>1</sup>, ZHANG Ting<sup>2</sup>, ZHANG Jian-ping<sup>1</sup>

(1. Laboratory of Nano-technology, Shanghai Nanotechnology Promotion Center, Shanghai 200237, China;

2. Laboratory of Nano-technology, Shanghai Institute of Microsystem and Information

Technology, Chinese Academy of Sciences, Shanghai 200050, China)

**Abstract:** The  $\text{Si}_2\text{Sb}_2\text{Te}_5$  (SST) array was fabricated by UV-imprint lithography (UV-IL) instead of optical lithography and PCRAM memory cell with  $18 \text{ M}/\text{Inch}^2$  was constructed, the array is the size of 2 inches. Memory switching from high resistance state to low resistance state has been achieved, with a resistance ratio of 30 has been achieved. In typical I-V curve, display threshold voltage to be 1.18 V. Structural transformation of SST film in heating process was in situ studied by means of time-resolved X-ray diffraction. This shows that the SST material phase change occurred in the range of  $200^\circ\text{C} \sim 300^\circ\text{C}$ .

**Key words:** UV - IL; SST array; PCRAM; memory cell

中文核心期刊

中国科技核心期刊

中国学术期刊综合评价数据库统计源期刊

俄罗斯《文摘杂志》(AJ.VINITI) 收录

美国《化学文摘》(CA) 收录

英国《科学文摘》(SA, INSPEC 数据库) 收录

美国《剑桥科学文摘》(CSA) 收录

美国《乌利希期刊指南》收录

ISSN 1671-4776

CN 13-1314/TN

CODEN WJEIAB

# 微纳电子技术

## Micronanoelectronic Technology

[Http://bdtq.chinajournal.net.cn](http://bdtq.chinajournal.net.cn)

[Http://wndzjs.periodicals.net.cn](http://wndzjs.periodicals.net.cn)

H&Z® HNZMEDIA.COM

中华人民共和国工业和信息化部主管

中国电子科技集团公司第十三研究所主办

### 勇攀三维技术高峰

1期

2009

第46卷 总第380期

### 让您的晶圆更有价值

第三维空间的成功依赖于技术的革新。SUSS技术在三维应用方面处于领先地位，利用创新的解决方案，研发出即可投入生产的三维工艺设备。我们致力于卓越的产品性能，协助您应对三维空间的挑战。

TSV硅通孔光刻

晶圆键合

薄晶圆处理

欢迎参观我们的展台

Semicon China, 2009年3月17-19日

中国 上海

W3展厅, 展台3000

## 压印技术制备超高密度 $\text{Si}_2\text{Sb}_2\text{Te}_5$ 基相变存储阵列

刘彦伯<sup>1,2</sup>, 闵国全<sup>1</sup>, 宋志棠<sup>2</sup>, 周伟民<sup>1</sup>,

张 静<sup>1</sup>, 张 挺<sup>2</sup>, 万永中<sup>1</sup>, 李小丽<sup>1</sup>, 张剑平<sup>1</sup>

(1. 上海市纳米科技与产业发展促进中心 纳米加工技术实验室, 上海 200237;

2. 中国科学院 上海微系统与信息技术研究所 纳米技术研究室, 上海 200050)

**摘要:** 采用低成本、高效率的压印技术实现了高密度相变存储器(PCM)存储阵列的制备, 开发出  $\text{Si}_2\text{Sb}_2\text{Te}_5$  (SST) 新材料的 4 G bit/inch<sup>2</sup> 存储阵列, 存储单元面积为  $0.04 \mu\text{m}^2$ ; 利用 SEM 观测压印获得的光刻胶图形阵列以及刻蚀后的 SST 存储阵列, 其单元外形均具有高度的一致性, 且单元特征尺寸的 3 倍标准差均小于 6 nm; 利用 AFM 研究了 SST 存储单元的 I-V 特性, 阈值电压为 1.56 V, 高、低电阻态阻值变化超过两个数量级。实验结果表明了 SST 新材料及压印技术在 PCM 芯片中的应用价值。

**关键词:** 紫外压印; 高密度相变存储器阵列;  $\text{Si}_2\text{Sb}_2\text{Te}_5$  存储单元; 标准差 ( $\sigma$ ); 相变

**中图分类号:** TN305 **文献标识码:** A **文章编号:** 1671-4776 (2009) 01-0045-05

### **$\text{Si}_2\text{Sb}_2\text{Te}_5$ Based Ultra-High-Density PCM Arrays Fabricated by UV-IL**

Liu Yanbo<sup>1,2</sup>, Min Guoquan<sup>1</sup>, Song Zhitang<sup>2</sup>, Zhou Weimin<sup>1</sup>,

Zhang Jing<sup>1</sup>, Zhang Ting<sup>2</sup>, Wan Yongzhong<sup>1</sup>, Li Xiaoli<sup>1</sup>, Zhang Jianping<sup>1</sup>

(1. Laboratory of Nano-Technology, Shanghai Nanotechnology Promotion Center, Shanghai 200237, China;

2. Laboratory of Nano-Technology, Shanghai Institute of Microsystem and Information Technology,

Chinese Academy of Sciences, Shanghai 200050, China)

**Abstract:** High-density phase change material arrays fabricated by a low cost and high efficient method were considered to be able to speed up research and development of the phase change random access memory (PCM), which was characteristic of low-voltage, low-power, fast reading/writing. The  $\text{Si}_2\text{Sb}_2\text{Te}_5$  (SST) based PCM array with density of 4 Gbit/inch<sup>2</sup> was fabricated by UV-imprint lithography (UV-IL), the PCM cell was with size of  $0.04 \mu\text{m}^2$ . Dimension stability of the array cell was analyzed with SEM, in each case, the  $3\sigma$  values was less than 6 nm. Due to the small size of PCM cell, I-V performance was measured by a conductive nano-tip on an atomic force microscope and the typical I-V curve of the cells was with a threshold voltage of 1.56 V. The resistance contrast of high-resistance state and low-resistance state is more than two orders according to the I-V curve. The results show that the SST and UV-IL have potential enormous application in the low-voltage, high-speed PCM chip.

收稿日期: 2008-09-09

基金项目: 国家重大科学研究计划资助项目 (2007CB935400); 上海市科研发计划 (0652nm052, 0752nm013, 0752nm014); 上海市博士后基金 (07R214204); 中国博士后基金 (20070420105)

E-mail: liuyanbo@snpc.org.cn

**Key words:** UV-imprint lithography (UV-IL); high-density phase change random access memory (PCRAM) arrays;  $\text{Si}_2\text{Sb}_2\text{Te}_5$  (SST) memory cell; standard deviation ( $\sigma$ ); phase change

**EEACC:** 7360P; 8130H

## 0 引言

相变存储器 (PCRAM) 是国际半导体协会路线图上下一代半导体存储器重要的候选，被业界认为是继 FLASH 后最有可能成为下一代商用的非挥发存储技术之一<sup>[1-6]</sup>。围绕低压、低功耗、高速、高密度存储器件商业化进程，PCRAM 迫切需要开发新材料、构建新结构，以减小相变区域、提高性能和集成度。其中相变材料 (PCM) 高密度阵列一致性制备是新型 PCRAM 集成开发的一个关键问题。

在新材料探索方面，一些性能比目前常用的  $\text{Ge}_2\text{Sb}_2\text{Te}_5$  优越的相变材料陆续被发现，例如  $\text{Si}_2\text{Sb}_2\text{Te}_5$ 。T. Zhang 等学者<sup>[7-8]</sup>的研究表明， $\text{Si}_2\text{Sb}_2\text{Te}_5$  (SST) 比  $\text{Ge}_2\text{Sb}_2\text{Te}_5$  具有更好的数据保持力和稳定性、更宽的禁带宽度和更低的阈值电流；Y. Zhang 等学者<sup>[9]</sup>也证明了 Si 掺杂  $\text{Sb}_2\text{Te}_3$  薄膜比  $\text{Ge}_2\text{Sb}_2\text{Te}_5$  薄膜具有更低的熔化温度和更高的晶态电阻，有利于降低 PCRAM 器件的 RESET 电流。这些成果反映出 SiSbTe 材料体系在高密度存储领域的潜在优势。

在新器件结构开发方面，特征尺寸减小对加工工艺要求越来越高。当器件结构进入 nm 尺度后，

采用电子束曝光、聚焦离子束和光学曝光等常规微细加工技术的开发成本急剧增加，尤其是新材料和新结构为稳定性能要优化参数，致使开发成本更高。而新兴的紫外压印 (UV-IL) 技术可以廉价地在大面积基片上重复、大批量地制备各种图形结构，具有成本低、效率高、精度高、尺寸一致性易于控制的综合优势<sup>[10-15]</sup>，将是解决新材料筛选和新器件结构开发中高成本低效率难题的有效途径之一。H. Lee 等学者<sup>[14]</sup>利用 UV-IL 在 Si 基钼层上制备了网架结构  $\text{Ge}_2\text{Sb}_2\text{Te}_5$  PCRAM 原型，线宽 60 nm；K. Y. Yang 等学者<sup>[15]</sup>在 Si 基上制作了  $\text{Ge}_2\text{Sb}_2\text{Te}_5$  点阵，最小尺寸 200 nm。目前该技术已趋成熟，最高水平实现 5 nm。

本文采用 UV-IL 技术制备  $\text{Si}_2\text{Sb}_2\text{Te}_5$ -PCRAM 高密度存储阵列，可以保证存储单元一致性，降低高密度器件开发成本、提高效率。同时，还可以有效检验新材料结构的按比例缩小性能、加速功能材料开发。对加快新相变材料筛选和高密度 PCRAM 开发具有重要意义。

## 1 实验

UV-IL 制作 SST 阵列流程如图 1 所示。

图 1 UV-IL 制作 SST 阵列流程示意图

Fig. 1 Schematic of SST array fabricated by UV-IL

预先在 Si 基 SiO<sub>2</sub>（经热氧化法生成，厚度 500 nm）表面用磁控溅射法依次沉积 Ti、TiN、SST 和 TiN，厚度分别为 100、10、20、10 nm，制备图 1 (a) 所示样品。采用 TiN 是因为 TiN 与 SST 材料具有相对较好的黏附力。

压印前，首先通过气相沉积法在模板表面形成一层全氟癸烷基三氯硅烷（silane、1H、1H、2H、2H-perfluorodecyltrichlorosilane (CF<sub>3</sub> - (CF<sub>2</sub>)<sub>7</sub> - (CH<sub>2</sub>)<sub>2</sub> - SiC<sub>6</sub>），FDTS）自组装膜。整个修饰过程在充满 N<sub>2</sub> 保护的手套箱内进行。

接着在样品表面涂一层黏合剂进行预处理；然后，旋涂紫外压印胶 AMONIL MMS4 (AMO, GmbH, 德国) 230 nm，如图 1 (b)。涂覆黏合剂和压印胶后的样品分别置于电热板上 100 °C 热烘 1 min。最后，用 1 英寸 (2.5 cm) 石英模板在 EVG620 (EV Group, 奥地利) 上完成紫外压印工艺，压印力和曝光时间为 60 kPa、100 s，如图 1 (c)、(d)。

压印后，用反应离子刻蚀 (RIE) 优化工艺首先去除残留胶，然后用不同工艺依次刻蚀 TiN、SST、TiN 层，如图 1 (e)、(f) 所示，实验在 MS-350 (ROTH & RAU, 德国) 上进行。

高密度存储阵列单元特征尺寸和存储单元的 I-V 特性分别通过 SEM (S-4800, Hitachi, 日本) 和 NTEGRA Prima SPM (NT-MDT, 俄罗斯) 进行表征。

## 2 结果和讨论

### 2.1 阵列加工

压印过程中模板结构与压印胶深度接触、挤压成型，致使模板与压印胶分离（脱模）时黏附力很大，极易发生粘连，所以压印前降低精密石英模板的表面能以减小黏附力非常重要。

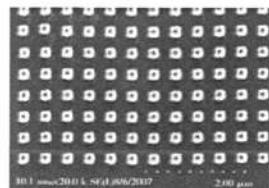

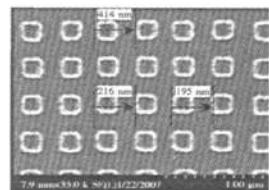

采用 FDTS 修饰后的石英模板（见图 2 (a)）压印脱模时模板与压印胶完全分离，且无剥离脱胶现象，获得了结构完整、边缘平滑的 AMONIL MMS4 阵列如图 2 (b) 所示。实验结果充分说明气相沉积法形成的自组装单层膜 (SAM) 显著降低了大比表面积石英模板的表面能，大大减小了模板与光刻胶之间的黏附力，有效解决了脱模时粘连的难题。另外，修饰后石英模板表面水滴接触角由

33.01°增大到 113.11°的实验结果，也充分验证了气相法 FDTS 修饰的有效性。均匀完整的 MMS4 阵列，说明预处理工艺有效提高了光刻胶成膜均匀性及膜与基底的黏附性。MMS4 阵列表面光洁、无气孔残留说明了压印前热烘工艺的有效性。

(a) 修饰后的石英模板

(b) AMONIL MMS4

(c) SST

图 2 高密度阵列 SEM 图像

Fig. 2 SEM images of high-density array

压印胶残留是压印光刻与传统光学光刻的一个显著区别，能否完全去除残留胶，对保证后续器件工艺和电学性能稳定尤为重要，因此，有效去除压印胶残留层是压印加工的一个关键问题。实验用 O<sub>2</sub>/Ar 混合等离子体优化刻蚀工艺，过刻蚀 10 nm，完全去除了 AMONIL MMS4 残留层。对功率和混合气体流量 (CF<sub>4</sub>/O<sub>2</sub> 和 CF<sub>4</sub>/Ar) 等 RIE 刻蚀参数的优化有效保证了转移精度，最终在 Ti/TiN 电极层上获得了 4 Gbit/inch<sup>2</sup> 的高密度 SST 点阵如图 2 (c) 所示。

SEM 观察的模板、MMS4 和 SST 阵列单元特征尺寸均值和 3 倍标准差 (3σ) 分别为 208.7、4.7 nm，195.4、5.0 nm，209.7、5.5 nm。上述均值分别是模板、MMS4 和 SST 阵列中均匀分布的

5个采样区域内不同位置对应的 $25(5 \times 5)$ 个单元特征尺寸的SEM平均值，见表1。 $3\sigma$ 值均小于6 nm，说明存储单元具有高度一致性。

表1 特征尺寸测量值概要

Table 1 Summary of the measured values of the critical dimension

| 阵列单元特征尺寸/nm | 最小值 | 最大值 | 均值    | $\sigma$ | $3\sigma$ |

|-------------|-----|-----|-------|----------|-----------|

| 模板          | 206 | 214 | 208.7 | 1.568    | 4.705     |

| MMS4        | 192 | 199 | 195.4 | 1.660    | 4.980     |

| SST         | 204 | 215 | 209.7 | 1.837    | 5.513     |

模板修饰和压印胶固化、高温形变以及刻蚀工艺等因素都会影响结构特征尺寸，因此，继续优化压印、蚀刻工艺有望进一步提高存储阵列的加工精度和一致性。

## 2.2 SST-PCRAM 存储单元电学特性

PCRAM 基于焦尔热作用下相变材料在非晶态和多晶态之间发生的可逆相变，利用相变材料非晶态的高电阻和多晶态的低电阻实现信息存储<sup>[16]</sup>。

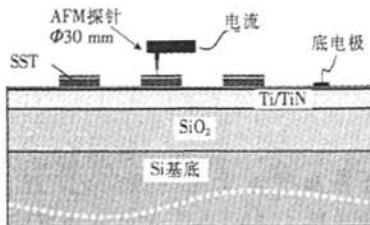

制造出的存储单元特征尺寸为 209.7 nm，周期为 400 nm，可在 AFM 设备上利用导电的纳米探针检测 SST 基 PCRAM (SST-PCRAM) 单元的电阻转换特性。图 3 为 SST-PCRAM 存储系统结构示意图，SST 单元与上、下电极的接触面积是  $0.04 \mu\text{m}^2$ ，如前所述，TiN、SST、TiN 和 Ti 层厚度分别为 10、20、10、100 nm。实验用探针尖端有金刚石膜，曲率半径 30 nm，传导率  $1 \Omega \cdot \text{cm}$ 。

图 3 SST-PCRAM 结构示意图

Fig. 3 Schematic of the SST-PCRAM structure

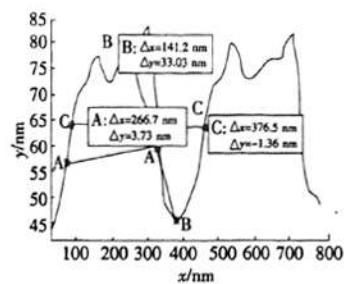

图 4 为在线扫描的 SST-PCRAM 阵列单元特征廓线，由图可见，存储单元半高宽 266 nm、半高周期 376 nm、高 33 nm，结果与前述 SEM 数据吻合。33 nm 的单元高度证明已经刻蚀到 Ti/TiN 层，印证了前述加工结论。

图 4 存储单元 AFM 外形廓线

Fig. 4 AFM contour of the storage cell

在线性变化的电压信号 ( $0 \sim 2.2 \text{ V}$ ,  $0.5 \text{ s}$ ) 激励下，SST-PCRAM 存储单元的典型 I-V 特性如图 5 所示：初始阶段电流很小 ( $0.1 \text{ nA}$  左右)，表明此时存储单元电阻很大，处于高阻态。当电压超过  $1.56 \text{ V}$  时，I-V 曲线发生突变，电流显著增加，说明电阻值急剧减小，转为低阻态。因为随着两端电压增加，SST 单元积聚的焦尔热逐渐增加，最终促使 SST 键合缺陷或多晶相生成而导致临界电流路径形成<sup>[9]</sup>，而临界路径一旦形成，电阻值显著减小，电流增大，SST 大量结晶。回扫描过程处于低阻态，电流随电压近似于线性变化，说明各膜层之间是良好的欧姆接触，压印、脱模和刻蚀过程没有影响膜层接触质量，蚀刻转移后去胶完全，保证了良好的接触。由图 5 可知，当电压为  $1.0 \text{ V}$  时，两条曲线对应的高、低阻变化达 140 倍，可满足 PCRAM 和电探针存储器应用需要。图中电流较小的原因有 AFM 探针涂敷了一层金刚石膜，传

图 5 SST-PCRAM 单元的 I-V 特性

Fig. 5 I-V characteristics of SST-PCRAM cell

导率约  $1 \Omega \cdot \text{cm}$ ；AFM 探针尺寸较小等。详细的研究正在进行中，包括膜厚、AFM 探针传导率和绝缘层涂敷参数的最优化等。

通过实验较好地实现了存储单元从高阻到低阻的转换。从低阻到高阻的转换特性对 PCRAM 同样重要，因在 AFM 测试系统中不能施加电脉冲，暂时未能实现从低阻到高阻的转换测试，相关工作正在进行中。

### 3 结 论

本文针对高密度 PCRAM 芯片的开发，开展了低成本、高效率的压印技术制备新型相变材料体系高密度存储阵列的关键技术研究，在 TiN/Ti 电极层上制备了 4 Gbit/inch<sup>2</sup> 的 SST 基超高密度存储阵列，存储单元面积为  $0.04 \mu\text{m}^2$ ；SEM 观察了阵列单元的高度一致性，其特征尺寸  $3\sigma$  均小于 6 nm；AFM 探针检测了存储单元 I-V 特性，阈值电压 1.56 V，且高、低阻变化达 140 倍。结果表明，SST 材料可在存储单元为 200 nm 尺度范围内的存储器件中应用，为高密度 SST-PCRAM 开发提供了实验依据。继续优化压印和刻蚀工艺可进一步提高阵列密度，完善结构和测试环境可进一步研究存储单元的可逆相变特性，加速 nm 尺度新材料、新结构器件研发进程。

### 参考文献：

- [1] BALASHOV A G, BALAN N N, KALININ A V, et al. Non-volatile phase change memory and its fabrication technology [C] //8<sup>th</sup> International Siberian Workshop and Tutorial on EDM2007. Erkagol, Altai, 2007: 121–122.

- [2] ZHANG Y, WONG H S P, RAOUX S, et al. Phase change nanodot arrays fabricated using a self-assembly diblock copolymer approach [J]. *Appl Phys Lett*, 2007, 91 (1): 013104 – 1 – 013104 – 3.

- [3] ZHANG T, SONG Z T, WANG F, et al. Advantages of SiSb phase-change material and its applications in phase-change memory [J]. *Appl Phys Lett*, 2007, 91 (22): 222102 – 1 – 222102 – 3.

- [4] ZHANG T, SONG Z T, WANG F, et al. Te-free SiSb phase change material for high data retention phase change memory application [J]. *J J Appl Phys*, 2007, 46 (25): L602 – L604.

- [5] ZHANG T, SONG Z T, LIU B, et al. Investigation of compositional gradient phase change  $\text{Si}_2\text{Sb}_2\text{Te}_3$  thin films [J]. *J J Appl Phys*, 2007, 46 (3): L70 – L73.

- [6] LEE S H, JUNG Y, AGARWAL R. Highly scalable non-volatile and ultra-lowpower phase-change nanowire memory [J]. *Nature Nanotechnology*, 2007, 2 (10): 626 – 630.

- [7] ZHANG T, CHENG Y, SONG Z T, et al. Comparison of the crystallization of Ge-Sb-Te and Si-Sb-Te in a constant-temperature annealing process [J]. *Scripta Materialia*, 2008, 58 (11): 977 – 980.

- [8] ZHANG T, SONG Z T, RAO F, et al. High speed chalcogenide random access memory based on  $\text{Si}_2\text{Sb}_2\text{Te}_3$  [J]. *J J Appl Phys*, 2007, 46 (11): L247 – 249.

- [9] ZHANG Y, FENG J, ZHANG Z F, et al. Characteristics of Si-doped  $\text{Sb}_2\text{Te}_3$  thin films for phase-change random access memory [J]. *Appl Surf Sci*, 2008, 254 (17): 5602 – 5606.

- [10] KO S H, PARK I, PAN H, et al. Direct nanoimprinting of metal nanoparticles for nanoscale electronics fabrication [J]. *Nano Lett*, 2007, 7 (7): 1869 – 1877.

- [11] LEE J J, CHOI K B, KIM G H, et al. The UV-nanoimprint lithography equipment with multi-head imprinting unit for sub-50 nm half-pitch patterns [J]. *Microelectronic Engineering*, 2007, 84 (5 – 8): 963 – 966.

- [12] CHOU S Y, KELMEL C, GU J. Ultrafast and direct imprint of nanostructures in silicon [J]. *Nature*, 2002, 417 (20): 835 – 837.

- [13] CHOU S Y, KRAUSS P R, RENSTROM P J. Imprint lithography with 25-nanometer resolution [J]. *Science*, 1996, 272 (5258): 85 – 87.

- [14] LEE H, HONG S H, YANG K Y, et al. Fabrication of  $\text{Ge}_2\text{Sb}_2\text{Te}_3$  based PRAM device at 60 nm scale by using UV nanoimprint lithography [J]. *Microelectronic Engineering*, 2007, 84 (4): 573 – 576.

- [15] YANG K Y, HONG S H, KIM D K, et al. Patterning of  $\text{Ge}_2\text{Sb}_2\text{Te}_3$  phase change material using UV nano-imprint lithography [J]. *Microelectronic Engineering*, 2007, 84 (1): 21 – 24.

- [16] ZHANG T, SONG Z T, LIU B, et al. Investigation of phase change  $\text{Si}_2\text{Sb}_2\text{Te}_3$  material and its application in chalcogenide random access memory [J]. *Solid-State Electronics*, 2007, 51 (6): 950 – 954.

### 作者简介：

刘彦伯（1968—），男，博士，副教授，从事微纳米加工技术及微纳电子器件开发研究工作。

# 机电一体化 Mechatronics

10

2008年10月

ISSN 1007-080X

CN 31-1714/TM

邮发代号 4-565

jdyt2007@126.com

Vol.14, No.10

封面人物

东方电气股份有限公司副总裁

东方电气集团东方电机有限公司总经理

韩志桥

中国装备 装备世界

主编观点 金融危机波及实业 机床贸易应走高端路线

人物访谈 永远被复制却从未被超越——起承转合：图尔克的中国发展之路

专题 我国环保设备发展现状及分析

学术论文 基于量子框架的汽车电控系统软件总线研究

代价参考粒子滤波在故障诊断中的应用

基于ARM和Linux的嵌入式Web Server设计与实现

电动轮耐久性试验台架的开发

POD推进器水动力性能模拟与分析

特别关注

## 机床企业再制造 探索特色新模式

Machine Tool Enterprises Remanufacturing

to Explore Characteristically New Pattern

定价：11.5元

专注中国机电行业

创新发展