# Control of the Interfacial Layer Thickness in Hafnium Oxide Gate Dielectric Grown by PECVD

Kyu-Jeong Choi, Jong-Bong Park, and Soon-Gil Yoon<sup>z</sup>

Department of Materials Engineering, Chungnam National University, 305-764 Daejon, Korea

The  $HfO_2$  thin films for use in gate dielectric applications were deposited at  $300^{\circ}C$  onto p-type Si(100) substrates using  $Hf[OC(CH_3)_3]_4$  as the precursor in the absence of oxygen by plasma-enhanced chemical vapor deposition (PECVD). The  $HfO_2$  films deposited in the absence of  $O_2$  show excellent electrical properties such as low equivalent oxide thickness (EOT) and good thermal stability. The deposited films have an interfacial layer of approximately 10 Å in thickness, resulting in a decrease in the thickness of the interfacial layer by about 50% compared to films deposited in the presence of oxygen. The leakage current density of  $HfO_2$  films was approximately four orders of magnitude lower than an electrically comparable  $SiO_2$  at the same EOT. The improvement of electrical properties can be attributed to the decrease in the  $SiO_2$  interfacial layer. The thickness of the interfacial layer can be controlled by deposition in the absence of oxygen after evacuation of the reaction chamber by means of an ultrahigh vacuum.

© 2003 The Electrochemical Society. [DOI: 10.1149/1.1556052] All rights reserved.

Manuscript submitted February 11, 2002; revised manuscript September 12, 2002. Available electronically February 28, 2003.

Considerable interest has developed in the replacement of dielectrics for use  $SiO_2$  in metal-oxide-semiconductor (MOS) devices in which the channel lengths are less than 100 nm. The intent is to phase out conventional  $SiO_2$  and oxynitrides due to excessive leakage current and reliability concerns. Alternative gate insulators with a higher electrical permittivity than  $SiO_2$  are currently under widespread investigation for use in future generations of MOS transistors. Thus, high dielectric constant thin films offer the potential of increased capacitance in physically thicker films, thus providing a possible way to reduce direct tunneling. Due to their thermodynamic stability, when in contact with silicon,  $HfO_2$  and its silicates have attracted considerable attention recently. In addition,  $HfO_2$  is compatible with a polysilicon gate without any barrier materials.

Thus far, HfO<sub>2</sub> thin films have been prepared by sputtering<sup>3,6</sup> as well as thermal chemical vapor deposition (CVD).5 The thermal CVD method has been reported to be successful in producing usable HfO<sub>2</sub> thin films at temperatures above 500°C using Hf[OC(CH<sub>3</sub>)<sub>3</sub>]<sub>4</sub> and O<sub>2</sub>. A lower deposition temperature for processing the HfO<sub>2</sub> thin films is necessary in order to avoid the formation of SiO<sub>2</sub> at the HfO2/Si interface. Compared with thermal CVD, the plasmaenhanced chemical vapor deposition (PECVD) technique has the advantage of deposition at as low temperatures a possible. However, an amorphous interfacial layer having a thickness of about 20 Å was formed at the HfO2/Si interface because, at the initial stage of deposition, the Si substrate was exposed to an O<sub>2</sub> ambient.<sup>7</sup> Another route to decrease the thickness of SiO2 is to deposit HfO2 films in the absence of O<sub>2</sub> after evacuating the chamber using an ultrahigh vacuum (10<sup>-6</sup> Torr) because the Hf[OC(CH<sub>3</sub>)<sub>3</sub>]<sub>4</sub> precursor itself contains the necessary oxygen to form HfO2. Such a method has the potential for controlling interfacial layer thickness during the deposition of HfO<sub>2</sub> thin films.

In this study, a hafnium oxide gate dielectric was deposited at 300°C using PECVD in the absence of  $\rm O_2$  after evacuating the chamber using an ultrahigh vacuum ( $\rm 10^{-6}$  Torr). The electrical properties of the Pt/HfO<sub>2</sub>/Si capacitors were found to be improved as a result of controlling the interfacial layer thickness of the HfO<sub>2</sub>/Si structures.

# **Experimental**

After standard cleaning of p-type Si(100) wafers (6-9  $\Omega$  cm resistivity),  $HfO_2$  films were deposited by PECVD using hafnium tertiary-butoxide ( $Hf[OC(CH_3)_3]_4$ , Techno Semichem Co., Ltd.) as the precursor in the absence of  $O_2$ . The reaction chamber before

<sup>z</sup> E-mail: sgyoon@cnu.ac.kr

HfO<sub>2</sub> deposition was evacuated (10<sup>-6</sup> Torr) using a diffusion pump in order to remove the residual oxygen in the chamber because its presence leads to the oxidation of the silicon surface at a deposition temperature of 300°C. In order to avoid the damage at the Si/HfO<sub>2</sub> interface by plasma, thermal deposition of HfO<sub>2</sub> without plasma was performed at the initial stage (around 1 min) and then deposition by plasma was performed after 1 min. The deposition conditions were performed at a temperature of 300°C, a pressure of 0.5 Torr, and an rf power of 40 W. The precursor was vaporized in a bubbler maintained at 30°C and was carried to the reactor using argon (purity 99.9999%) as the carrier gas. The Pt top electrodes for measurement of the electrical properties were patterned using lift-off lithography. The capacitor area for the MOS (Pt/HfO2/Si) structure was 2  $\times$  10<sup>-5</sup> cm<sup>2</sup>. After patterning the electrode, the samples were annealed at various temperatures ranging from 600 to 900°C in N2 (purity 99.9999%) for 60 s. The physical thickness of the HfO<sub>2</sub> thin film was measured using high-resolution transmission electron microscopy (TEM, CM20T/STEM, Philips). The composition of HfO<sub>2</sub> films was determined by Rutherford backscattering spectroscopy (RBS, NEC 3SDH, 2.240 MeV 4He<sup>++</sup>). The capacitance-voltage (C-V) and current-voltage (I-V) were measured using an HP4194A impedance/gain-phase analyzer and an HP4145B semiconductor parameter analyzer, respectively.

## **Results and Discussion**

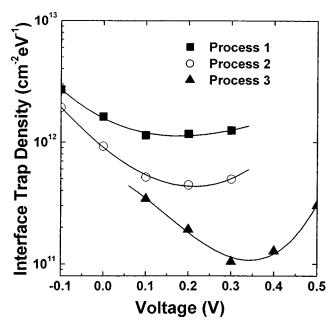

Figure 1 shows the variation of interface trap density as a function of applied voltage in order to confirm the effect of Ar plasma damage on HfO<sub>2</sub> thin film growth. As shown in Fig. 1, thin films prepared by process 3 showed the lowest interface trap density compared with those by processes 1 and 2. These results suggested that the deposition (process 3) performed in this study effectively alleviated the plasma damage in Si/HfO<sub>2</sub> interface.

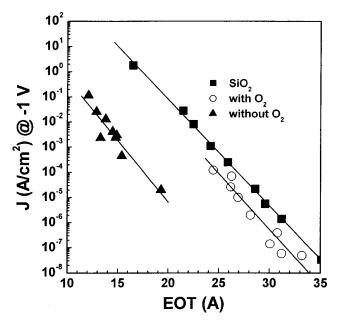

Figure 2 shows the variation of the equivalent oxide thickness (EOT) of  $HfO_2$  films as a function of leakage current density, as measured at -1 V. The relationship between EOT and the leakage current of the  $SiO_2$  films is also shown as a comparison with the  $HfO_2$  films (solid square). The leakage current density of the  $HfO_2$  films deposited in the presence of  $O_2$  varied with a tendency similar to that of  $SiO_2$  and was approximately one order of magnitude lower than  $SiO_2$  at the same EOT. This suggests that interfacial layers above 20 Å in thickness were formed at the  $HfO_2/Si$  interface and that they play an important role in the characteristics of the leakage current of  $Pt/HfO_2/Si$  capacitors. The leakage current density of  $HfO_2$  films deposited in the absence of  $O_2$  is approximately four orders of magnitude lower than  $SiO_2$  at the same EOT.

**Figure 1.** Interface trap densities of Pt/HfO<sub>2</sub> /Si capacitors as a function of applied voltage. Process 1, keeping Si substrate in Ar plasma ambient for 1 min→HfO<sub>2</sub> deposition for 6 min in Ar plasma ambient. Process 2, thermal deposition (without plasma) of HfO<sub>2</sub> for 1 min→making vacuum ambient→keeping 1 min in Ar plasma→HfO<sub>2</sub> deposition for 5 min in Ar plasma. Process 3, thermal deposition of HfO<sub>2</sub> for 1 min→HfO<sub>2</sub> deposition for 5 min in Ar plasma ambient.

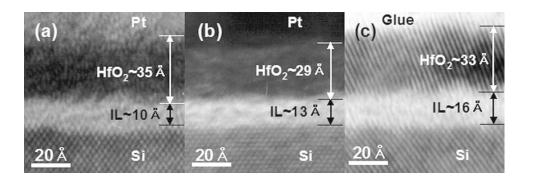

The HRTEM images of as-deposited and annealed Pt/HfO<sub>2</sub>/Si samples at 900°C for 60 s in a nitrogen ambient are shown in Fig. 3. Figure 3c shows the image of a HfO<sub>2</sub>/Si structure annealed at the same condition without a top Pt. As shown in Fig. 3a and b, the total physical thickness of as-deposited and annealed films was approximately 45 and 42 Å, respectively. Even though the thickness of the interfacial layer is not clear because of the reaction between Hf, O, and Si, the 10 Å thick interfacial layers in the as-deposited films increased by approximately 13 Å as the result of annealing at 900°C in the nitrogen ambient. The annealed HfO<sub>2</sub> films showed a decrease in thickness because of their more dense crystalline nature. The densification of pure oxide materials is dependent on the complete removal of oxygen vacancies if volatile elements are absent in the bulk materials. The HfO<sub>2</sub> films shown in Fig. 3c showed a higher crystallinity than that of the films shown in Fig. 3b. The interfacial layer thickness of the HfO<sub>2</sub>/Si structure (shown in Fig. 3c) increases more than that of the Pt/HfO<sub>2</sub>/Si structure because the top Pt layer suppresses the diffusion of oxygen into the SiO<sub>2</sub> layer in a nitrogen ambient anneal. Any annealing treatments which have an excess of oxygen present will lead to the rapid diffusion of oxygen through the oxides, resulting in SiO or SiO<sub>2</sub>-containing interface layers. When Fig. 3b is compared with Fig. 3c, the interfacial layer thickness by

Figure 2. Leakage current density of  $Pt/HfO_2/Si$  capacitors as a function of EOT.  $HfO_2$  films deposited in the presence of and absence of  $O_2$  are compared with  $SiO_2$ .

oxygen contained in the nitrogen can be reduced by the deposition of the Pt top electrode before the annealing of HfO<sub>2</sub> films.

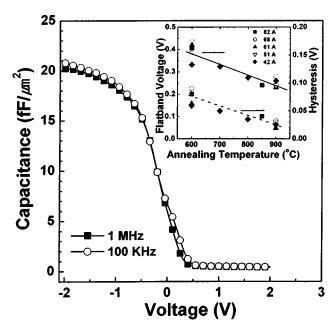

Figure 4 shows the frequency dependence on the C-V characteristics of Pt/HfO2/Si structures annealed at 900°C for 60 s in a N2 ambient. The Pt/HfO2/Si structures show clear accumulation, depletion, and inversion regions. The EOT values were extracted from the accumulation capacitance of 1 MHz C-V curves and include the quantum mechanical deduction using the North Carolina State University CVC program. 10 The EOT and the effective dielectric constant of the Pt/HfO2/Si capacitors annealed at 900°C were approximately 14.8 Å and 11.1, respectively. A slight frequency dependent hump of capacitance near 0 V was observed in the capacitancevoltage relationship measured at 100 kHz, consistent with originating from interface traps. 11 The inset in Fig. 4 shows the relationship between the flatband voltage and hysteresis of Pt/HfO2/Si capacitors for various film thicknesses as a function of annealing temperature for 60 s in  $N_2$  ambient. The flatband voltage ( $V_{\rm FB}$ ) was determined from the intercept of the  $1/C^2$  vs. V plot. <sup>12</sup> The  $V_{\rm FB}$  slightly decreased with increasing annealing temperature irrespective of film thickness. As-deposited  $HfO_{2+x}$  (x = 0.2, approximately) films containing an excessive oxygen from RBS analysis preserve the negative charges and then produce a shift in the value of  $V_{\rm FB}$  toward a positive voltage. The excessive oxygen decreased with an increase of annealing temperature in a  $N_2$  ambient (approximately  $P_{O_2}$  $\approx 10^{-3}$  Torr) and the decrease in negative charges shifted the  $V_{\rm FB}$

**Figure 3.** Cross-sectional HRTEM images of (a) as-deposited and (b) annealed  $Pt/HfO_2/Si$  capacitors, (c) annealed  $HfO_2/Si$  structures at 900°C in  $N_2$  for 60 s.

**Figure 4.** Capacitance vs. voltage characteristics of Pt/HfO<sub>2</sub>/Si capacitors annealed at 900°C in a N<sub>2</sub> ambient for 60 s. Inset shows the relationship between flatband voltage and hysteresis as a function of annealing temperature at 1 MHz

toward a negative gate voltage, resulting in a decrease in flatband voltage with increasing annealing temperature in the  $N_2$  ambient. The hysteresis due to charge trapping was reduced with increasing annealing temperature and, in samples annealed at  $900^{\circ} C$  was reduced to a negligible level of about 25 mV. This result is comparable to that of  $HfO_2$  films deposited by reactive dc magnetron sputtering.  $^{13}$

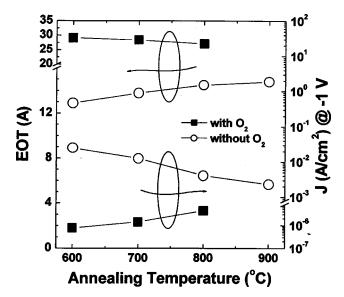

Figure 5 shows the relationship between the EOT and the leakage current density of  $Pt/HfO_2/Si$  capacitors annealed at various temperatures in  $N_2$  for 60 s. The electrical properties of  $HfO_2$  films deposited in the absence of oxygen were compared with those of

Figure 5. The EOT vs. leakage current density of  $Pt/HfO_2/Si$  capacitors as a function of annealing temperature in a  $N_2$  ambient.

films deposited in the presence of oxygen. The EOT and leakage current of films deposited in the presence of oxygen showed a reverse tendency, as compared with those in the absence of oxygen. The thickness of the SiO<sub>2</sub> interfacial layer in films annealed at 800°C in a N<sub>2</sub> ambient did not change with respect to that of films as-deposited with oxygen gas because the SiO<sub>2</sub> layer is sufficient to resist the penetration of oxygen. The decrease in thickness of HfO<sub>2</sub> films irrespective of an SiO2 interfacial layer thickness plays a critical role in the decrease in EOT with increasing annealing temperature. On the other hand, the EOT of HfO<sub>2</sub> thin films deposited in the absence of oxygen increased with increasing annealing temperature in the  $N_2$  ambient. The reason for this is that the  $SiO_2$  interfacial layer rather than the HfO<sub>2</sub> films increased with increasing annealing temperature as shown in Fig. 3. The decrease of leakage current densities with annealing temperature in HfO<sub>2</sub> films deposited in the absence of oxygen can be attributed to the increase in the SiO<sub>2</sub> interfacial layer rather than an increase in leakage current by crystallization of the HfO2 thin films. On the other hand, the leakage currents of HfO2 thin films deposited in the presence of oxygen were governed by the crystallization of the HfO2 films since the thickness of SiO<sub>2</sub> interfacial layers remained unchanged for increasing annealing temperatures in the N2 ambient, resulting in an increase in leakage current with increasing annealing temperature.

#### Conclusions

Hafnium oxide thin films for use as gate dielectrics were deposited at 300°C on p-type Si(100) substrates using Hf[OC(CH<sub>3</sub>)<sub>3</sub>]<sub>4</sub> as the precursor in the absence of oxygen by plasma-enhanced chemical vapor deposition. Compared with HfO<sub>2</sub> films deposited in the presence of O<sub>2</sub>, the films deposited in the absence of O<sub>2</sub> show excellent electrical properties including low capacitance equivalent oxide thickness and good thermal stability. The HfO<sub>2</sub> films deposited in the absence of O<sub>2</sub> have an interfacial layer of approximately 10 Å in thickness, resulting in a decrease in the thickness of the interfacial layer by about 50% compared to films deposited in the presence of oxygen. The leakage current density of HfO<sub>2</sub> films deposited in the absence of O<sub>2</sub> is approximately four orders of magnitude lower than that of SiO<sub>2</sub> for the same EOT.

### Acknowledgments

This work was performed under the University Research Program supported by the Ministry of Information and Communication of South Korea. The authors thank the Techno Semichem Co., Ltd., for supplying the  $Hf[OC(CH_3)_3]_4$ .

Chungnam National University assisted in meeting the publication costs of this article.

## References

- 1. D. A. Buchanan, IBM J. Res. Dev., 43(3), 245 (1999).

- B. H. Lee, L. Kang, W. J. Qi, R. Nieh, Y. Jeon, K. Onishi, and J. C. Lee, Tech. Dig. - Int. Electron Devices Meet., 1999, 133.

- B. H. Lee, R. Choi, L. Kang, S. Gopalan, R. Nieh, K. Onishi, Y. Jeon, W. Qi, C. Kang, and J. C. Lee, Tech. Dig. Int. Electron Devices Meet., 39 (2000).

- 4. G. D. Wilk and R. M. Wallace, Appl. Phys. Lett., 74, 2854 (1999)

- S. J. Lee, H. F. Luan, W. P. Bai, C. H. Lee, T. S. Jeon, Y. Senzaki, D. Roberts, and D. L. Kwong, Tech. Dig. - Int. Electron Devices Meet., 2000, 31.

- L. Kang, K. Onishi, Y. Jeon, B. H. Lee, C. Kang, W. Qi, R. Nieh, S. Gopalan, R. Choi, and J. C. Lee, *Tech. Dig. Int. Electron Devices Meet.*, 35 (2000).

- 7. K. J. Choi, W. C. Shin, and S. G. Yoon, J. Electrochem. Soc., 149, F18 (2002).

- 8. B. Brar, G. D. Wilk, and A. C. Seaburgh, Appl. Phys. Lett., 69, 2728 (1996).

- 9. G. D. Wilk, R. M. Wallace, and J. M. Anthony, *J. Appl. Phys.*, **89**, 5243 (2001).

- J. R. Hauser and K. Ahmed, Characterization and Metrology for ULSI Technology, pp. 235-239, AIP, New York (1998).

- K. Fukuda, W. J. Cho, K. Arai, S. Suzuki, J. Senzaki, and T. Tanaka, Appl. Phys. Lett., 77, 866 (2000).

- D. K. Schroder, Semiconductor Material and Device Characterization, 2nd ed., pp. 349-350, John Wiley & Sons, New York (1998).

- B. H. Lee, L. Kang, R. Nieh, W. J. Qi, and J. C. Lee, Appl. Phys. Lett., 76, 1926 (2000).