## Characterization of 4H-SiC Epilayers Grown at a High Deposition Rate

H. Tsuchida<sup>1</sup>, T. Tsuji<sup>2</sup>, I. Kamata<sup>1</sup>, T. Jikimoto<sup>1</sup>, H. Fujisawa<sup>2</sup>, S. Ogino<sup>2</sup> and K. Izumi<sup>1</sup>

Central Research Institute of Electric Power Industry,

2-6-1 Nagasaka, Yokosuka, Kanagawa 240-0196, Japan

Fuji Electric Corporate Research & Development, Ltd.,

2-2-1 Nagasaka, Yokosuka, Kanagawa 240-0194, Japan

Keywords: DLTS, Epitaxial Growth, Photoluminescence, Schottky Diodes

Abstract Epitaxial 4H-SiC layers grown at 10-18 μm/h in a vertical radiant-heating reactor have been characterized in terms of their morphology, purity and device performance. Through optimizations of pre-growth hydrogen etching and growth parameters, a good morphology is reproducibly obtained even for thick layers. Photoluminescence and DLTS measurements have been performed for epitaxial layers to determine impurity levels and the intrinsic defect density, and the growth parameters required to obtain a low background doping and smooth surface are discussed. Edge-terminated Ni/4H-SiC Schottky barrier diodes have been fabricated, and electrical performance of the devices is demonstrated.

## 1. Introduction

Power electronics is a key technology for current and future power transmission and distribution systems, and recent progress in SiC crystal quality and device performance is making the electric power industry the focus of considerable attention. Electric power applications require high-power devices that can handle over several kV and over 100 A (or even over a few kA). Because high-voltage SiC devices need a thick active layer, techniques in SiC epitaxy to obtain a higher growth rate have been studied intensively. It has been reported that growth rates around 10 μm/h are available in a horizontal hot-wall reactor with uniform doping and thickness [1]. A vertical hot-wall reactor has achieved high growth rates of up to 30 μm/h with a specular surface [2]. High-voltage bipolar devices require a long minority carrier lifetime to realize a low on-state forward voltage-drop (V<sub>on</sub>), and crystallographic defects and impurity levels must be minimized. High power devices with a large active area also require minimizing of defects induced during epitaxial growth, as well as defects in the substrate. From this point of view, improving crystal quality while achieving a high growth rate with a sufficient wafer capacity is a challenge for current SiC epitaxy. In this paper, we report on the quality of epitaxial layers obtained at a high growth rate in a vertical radiant-heating reactor.

2. Experiments

Epitaxial growth was performed on commercial 8° off 4H-SiC(0001) substrates in a vertical radiant-heating reactor. Substrates and a susceptor were placed inside a cylindrical hot-wall, so that the substrates and the susceptor were heated by radiation from the hot-wall [3]. We used SiH<sub>4</sub> and  $C_3H_8$  as precursors with upward H<sub>2</sub> carrier gas flow. Typical growth temperature was 1530-1600°C at the susceptor top, although the hot-wall temperature was considerably higher than the susceptor temperature. Thick 4H-SiC epitaxial layers were grown at 10-18  $\mu$ m/h under a reduced pressure of as low as around 50 Torr.

Nomarski optical microscopy and atomic force microscopy (AFM) were used to examine the morphology of epitaxial layers. Low temperature photoluminescence (PL) measurements were performed at 8K using a He-Cd laser ( $\lambda$ =325 nm). The  $Z_1$  trap concentration was determined by deep level transient spectroscopy (DLTS) through fabricating Ni-Schottky electrodes. For the DLTS measurements, we applied the reverse bias of -10 V and pulse bias of 0 V for 100  $\mu$ s.

High-voltage 4H-SiC Schottky barrier diodes (SBD) were fabricated employing Ni as a Schottky metal. Edge termination for Schottky electrodes was achieved by a guard ring structure produced via B<sup>+</sup> implantation. Post-implantation annealing was carried out at 1050°C and 90 min

for the first lot and 1700°C and 30 min for the second lot. After the guard ring formation, Ni-Schottky electrodes were deposited on epitaxial layers through sputtering. Backside Ni ohmic contacts were made by annealing in Ar at 1050°C for 2 min.

(a) C/Si =0.77 (b) C/Si =0.85 380 385 390 395 400 Photon Wavelength (nm)

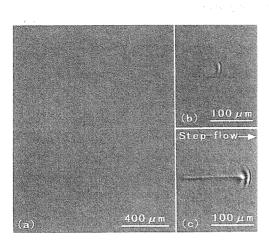

Fig. 1. Nomarski interference contrasts of a 90  $\mu$ m-thick 4H-SiC epitaxial layer grown at 18  $\mu$ m/h.

Fig. 2. Near band edge photoluminescence from epitaxial layers grown at (a) C/Si=0.77 and (b) C/Si=0.85 without intentional doping.

## 3. Results and discussions

3.1 Morphology and purity

First we examined growth pits on epitaxial layers. Figure 1 shows Nomarski contrasts of a 90 μm-thick epitaxial layer grown at 18 μm/h after hydrogen etching at 1400°C (measured for the susceptor top) for 45 min. After the hydrogen etching, epitaxial growth was performed at 1550°C under 50 Torr. A large defect free area without observable growth pits is shown in Fig. 1(a). A good morphology with low density of growth pits was obtained reproducibly by applying pregrowth hydrogen etching at 30 Torr, whereas applying hydrogen etching at 50-760 Torr tended to result in high density (typically 10<sup>3</sup>-10<sup>4</sup> cm<sup>-3</sup>) of growth pits, visible in Nomarski contrast at a low magnification. As this result, the pressure during hydrogen etching is a promising parameter to control growth pit density. An increase in the Si evaporation rate by reducing pressure, leading to inhibit Si enrichment or droplets on the etched surface [4], may be helping the reduction of growth pit density when applying hydrogen etching at 30 Torr. In addition, as shown in Fig. 1(a), traces of polishing-induced scratches are efficiently eliminated from layer surfaces. The most common growth pits remaining on epitaxial layers are wavy-pits [Fig.1 (b)], as classified in Ref. [5], and line-shaped pits [Fig. 1(c)]. Appearance and distribution of wavy-pits were not uniform throughout a sample. The typical density of wavy-pits is 10<sup>1</sup> cm<sup>-2</sup>, although the density reaches 10<sup>2</sup> cm<sup>-2</sup> range in some low-grade wafers. Line-shaped growth pits have a straight long depression parallel to the step-flow direction. Our KOH etching analysis revealed that most of the line-shape pits have screw type dislocations (1C screw dislocations and/or a micropipe) at the upstream end of the step-flow as described in detail in Ref. [6]. The both types of pits are presenting independently in most cases, whereas some of line-shaped pits accompany with a wavy pit at the downstream end as shown in Fig. 1(c). This implies that a disturbance of the step-flow is a possible origin of the wavy pit.

The purity of epitaxial layers was checked using PL measurements. Figure 2 shows near band edge spectra for epitaxial layers grown at C/Si=0.77 [spectrum (a)] and C/Si=0.85 [spectrum (b)] without intentional doping. The thickness of each layer was 54  $\mu$ m and 63  $\mu$ m, respectively. The PL spectra were recorded at a resolution of ~1 Å. Weak nitrogen bound excitons (Q<sub>0</sub>, P<sub>77</sub>) compared to free excitons (I<sub>77</sub>) suggest that the nitrogen incorporation levels are very low. Aluminum bound excitons and boron bound excitons are also very weak. Reduction of nitrogen incorporation levels as a result of the increasing C/Si ratio from 0.77 to 0.85 is confirmed by the

weakening of the nitrogen bound excitons in Fig. 2. Both layers were identified as n-type, and the net carrier densities  $(N_d-N_a)$  were determined as  $\sim 8\times 10^{13}$  cm<sup>-3</sup> for C/Si=0.77 and  $\sim 2\times 10^{13}$  cm<sup>-3</sup> for C/Si=0.85 at the center of the samples by C-V measurements. The capacitance of the Schottky diodes near the sample edge was not determined for the layer grown at C/Si=0.85, possibly due to an influence of wafer holder that was touching on the sample edge (growth face) along the gas C/Si=0.77 had a smooth surface without macro step bunching, whereas the layer grown at C/Si=0.85 exhibited deep grooves (stripe type defects) on the surface. To obtain a low background doping and a smooth surface at the same time, we adjust C/Si ratios from 0.77 to 0.80. Although the window for C/Si ratios is very narrow in this reactor, intentional n-type doping from low  $10^{15}$  to low  $10^{19}$  cm<sup>-3</sup> has been achieved under a constant C/Si ratio of 0.77.

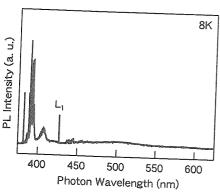

Figure 3 shows a wide-range PL spectrum for a layer doped intentionally to  $1.5\times10^{15}$  cm<sup>-3</sup>. The layer was grown at 15 µm/h under a C/Si ratio of 0.77, and the thickness was 120 µm. Aluminum- or boron-related donor-acceptor pair (DAP) and titanium lines are very weak, however, a defect related L<sub>1</sub> line (427.2 nm) is clearly seen. We also performed DLTS measurements, and the Z<sub>1</sub> trap concentration of a layer grown at C/Si=0.77 (growth rate: 14 µm/h, higher than the successful result in a conventional horizontal cold-wall reactor [7]. We suppose that reduction of the intrinsic defects while achieving a high growth rate is an additional technical scale with this reactor. The Z<sub>1</sub> trap concentration determined for the intentionally doped layer is comparable to the background N<sub>d</sub>-N<sub>a</sub> values for the layers appeared in Fig. 2. Since the Z<sub>1</sub> center acts in an acceptor-like manner, compensation by the Z<sub>1</sub> center must be taken into account to the layers without intentional doping.

Fig. 3. Photoluminescence from an intentionally doped layer grown at C/Si raio=0.77 (120  $\mu$ m-thick, 1.5  $\times$  10<sup>15</sup> cm<sup>-3</sup>).

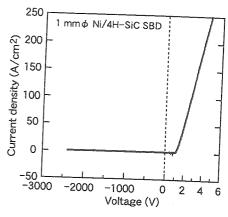

Fig. 4. I-V characteristic of a 1 mm  $\phi$  Ni/4H-SiC SBD fabricated on an epitaxial layer (27  $\mu$ m-thick,  $3 \times 10^{15}$  cm<sup>-3</sup>).

3.2 Device performance

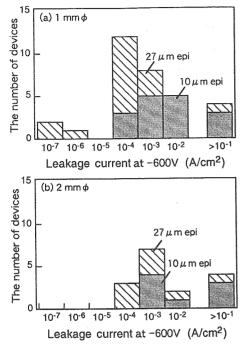

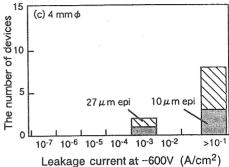

Electrical performance of epitaxial layers was examined by testing Ni/4H-SiC SBD. A 10  $\mu m$ -thick epitaxial layer doped intentionally to  $\sim\!\!7\times10^{15}$  cm  $^3$  was used in the first lot, and a 27  $\mu m$ -thick epitaxial layer doped intentionally to  $\sim\!\!3\times10^{15}$  cm  $^3$  in the second lot. These layers were grown at 14-16  $\mu m/h$ . The best breakdown voltage for 0.2 mm  $\phi$  SBD using the 10  $\mu m$  layer was 1.3 kV, even though the layer was grown in only 40 min. In use of the 27  $\mu m$  layer, a breakdown voltage of 2.4 kV was achieved for 1 mm  $\phi$  SBD as shown in Fig. 4. The on-resistance of the 2.4 kV SBD was 13.8 m  $\Omega$  cm² (V on =2.7 V at 100 A/cm²). Figure 5(a) shows a histogram of leakage current levels at -600 V for 1 mm  $\phi$  SBD. The corresponding electric field for -600 V is ~1.2 fabricated using the 27  $\mu m$  layer was able to block -600 V with a small leakage current density in the order of 10-7 A/cm², although the average leakage current density was rather high, probably due to fewer optimizations of process parameters and defect issues. The percentage of tolerable ones, that could block -600 V within a critical leakage current less than 1 mA, was over 85% for

1 mm  $\phi$  SBD. The percentage for 2 mm  $\phi$  SBD remained at a reasonable level of 75% as shown in Fig. 5(b). We confirmed large defect-free areas over 10 mm<sup>2</sup>, where no observable defects existed except wavy-pits, in microscope observation. This may be attributed to the high yield of 1-2 mm  $\phi$  SBD. In use of both the layers, we succeeded in obtaining 4 mm  $\phi$  SBD capable of blocking -600 V with a leakage current density in the order of  $10^{-3}$  A/cm<sup>2</sup>, however, about 80% of 4 mm  $\phi$  SBD resulted in failure within a very small reverse voltage [Fig. 5(C)]. To understand the poor yield of 4 mm  $\phi$  SBD, a density of  $10^{1}$  cm<sup>-2</sup> range for destructive defects is reasonable. This estimated density is close to the density of micropipes.

Fig. 5. Histograms of leakage current levels for (a) 1 mm  $\phi$  Ni/4H-SiC SBD, (b) 2 mm  $\phi$  SBD and (c) 4 mm  $\phi$  SBD at a reverse bias voltage of -600 V. The corresponding electric field for -600V is ~1.2 MV/cm for the 10  $\mu$ m layer and ~0.79 MV/cm for the 27  $\mu$ m layer.

Conclusions

We identified the characteristics of 4H-SiC epitaxial layers grown at 10-18  $\mu$ m/h in a vertical radiant-heating reactor. Reduction of epi-induced growth pits was achieved by applying pregrowth hydrogen etching under a reduced pressure as low as 30 Torr. Careful adjustment of the C/Si ratio is needed to obtain a low background doping and a smooth surface at the same time. Photoluminescence measurements showed low impurity levels for the layers. In use of a 27  $\mu$ m epitaxial layer, a breakdown voltage of 2.4 kV was achieved for 1 mm  $\phi$  Ni/4H-SiC SBD with an on-resistance of 13.8 m $\Omega$ cm² ( $V_{on}$ =2.7 V at 100 A/cm²). Some 1 mm  $\phi$  SBD showed a small leakage current density in the order of  $10^{-7}$  A/cm² at -600 V.

## References

[1] K.G. Irvine, R. Singh, M.J. Paisley, J.W. Palmour, O. Kordina, and C.H. Carter Jr., Mater. Res. Soc. Symp. 512 (1998), p. 119.

[2] A. Ellison, J. Zhang, W. Magnusson, A. Henry, Q. Wahab, J.P. Bergman, C. Hemmingsson, N.T. Son, and E. Janzén, Mater. Sci. Forum 338-342 (2000) p. 131.

[3] H. Tsuchida, I. Kamata, T. Jikimoto, and K. Izumi, Mater. Sci. Forum 338-342 (2000) p.145.

[4] A.A. Burk Jr., L.B. Rowland, J. Cryst. Growth 167 (1996) p. 586.

[5] A. Ellison, Doctoral thesis: Silicon Carbide Growth by high temperature CVD techniques, Dissertation No. 599, Linköping University, Sweden (1999).

[6] I. Kamata, H. Tsuchida, T. Jikimoto, and K. Izumi, this proceeding.

[7] T. Kimoto, A. Itoh, and H. Matsunami, Phys. stat. Sol. (b) 202 (1997) p. 247.