# Echelle grating WDM (de-)multiplexers in SOI technology, based on a design with two stigmatic points.

F. Horst\*a, William M.J. Greenb, B.J. Offreina, Yurii VlasovbalBM Zurich Research Laboratory, Rueschlikon, Switzerland;bIBM T.J. Watson Research Center, Yorktown Heights, NY 10598, USA

#### **ABSTRACT**

We present ultra-compact integrated optical echelle grating WDM (de-)multiplexers for on-chip optical networks. These devices are based on a design with two stigmatic points. The devices were fabricated using Silicon-On-Insulator (SOI) photonic waveguide technology thus the smallest version of the (de-)multiplexer occupies an area of only  $250x200~\mu m$ . We will show measurement results on different variations of the echelle grating devices. In the measurements, we found a channel to channel isolation of 19 dB. The minimum insertion loss, relative to a straight waveguide, is only 3 dB with a channel to channel variation of 0.5 dB.

Keywords: Silicon on Insulator, SOI, grating, echelle, demultiplexer, optical, WDM

# 1. INTRODUCTION

The echelle grating device that is presented in this study has been developed as a building block for on-chip optical Dense or coarse WDM networks. For this application, the device should be reproduced on the chip many times, thus the size of the device should be as small as possible, and the demultiplexing characteristics should be very reproducible from device to device. The wavelength specifications for the demultiplexer were set at follows: The device should demultiplex 8 channels with a channel spacing of 3.2 nm and the center wavelength for the filter spectrum was set at 1550 nm.

There are a number of wavelength demultiplexer designs that lend themselves to on-chip integration with CMOS integrated circuits and which could reach the above specifications. Among these are devices based on ring resonators [1], cascaded Mach-Zehnder interferometers [2], arrayed waveguide gratings [3] and echelle grating devices [4].

The response of ring resonator and cascaded Mach-Zehnder devices strongly depends on the correct optical path length of single waveguides within the devices, and is therefore sensitive to local process variations. In the arrayed waveguide grating this effect is already reduced due to the averaging effect over the many waveguides that shape the response. However, the effect is expected to be lowest in the echelle grating, because in the part of this device that shapes the filter response, the light travels in a slab waveguide or "free space" region and is laterally not confined by waveguides at all. Also the response is formed by reflection on many grating "teeth", which achieves an averaging effect, as is the case with the arrayed waveguide grating. Another important consideration is that, for the same response, an echelle grating device can be significantly smaller than an arrayed waveguide grating device.

A disadvantage of echelle grating devices is that a very good control of the vertical etch step of the diffraction grating is needed to prevent losses by scattering or by reflection of light downward into the substrate [5]. However, due to the large numerical aperture of SOI waveguides, these requirements are relaxed in this technology, and previous results on our SOI waveguides show that our technology exhibits a very good quality of the etched facets [6], [7], [8].

# 2. DEVICE LAYOUT

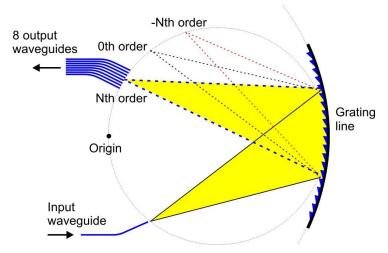

#### 2.1 Basic echelle grating

Figure 1 shows a schematic drawing of a basic echelle grating demultiplexer. In the bottom left of the figure, light from an input waveguide enters the "free space" region, where there is no lateral confinement, and the light can freely diverge. At the end of the free space region, the divergent beam is intercepted and reflected by the etched-down grating line. Due to the interference between the reflections from the different grating "teeth" or mirrors, the light is reflected into various grating orders. By "blazing", or adjusting the tilt of the grating mirrors, the majority of the reflected light can be directed into one, desired, reflection order. Due to the curvature of the grating line, the reflected beam converges and is refocused onto a row of output waveguides. The reflection angle of the higher order grating mode is wavelength dependant, thus

Silicon Photonics and Photonic Integrated Circuits, edited by Giancarlo C. Righini, Seppo K. Honkanen, Lorenzo Pavesi, Laurent Vivien, Proc. of SPIE Vol. 6996, 69960R, (2008) · 0277-786X/08/\$18 · doi: 10.1117/12.781232

the position of the focus will move along the row of waveguides and, depending on wavelength, select different output waveguides.

Figure 1: Basic echelle grating layout

#### 2.2 Design with two stigmatic points

The basic echelle grating layout that is drawn in Figure 1 is based on the commonly used "Rowland mounting": This type of echelle grating layout is often used because it is easy to construct and has good performance: The grating line follows a circle with radius R around a given origin, the grating has equidistant spacing between the grating teeth and the input and output waveguides lie on a second circle with radius R/2, which touches the grating line and the origin. Also, the reflection focus is free of coma and has low spherical aberration.

However, for the design of the current demultiplexer in SOI technology, there is no reason to limit ourselves to equidistant grating teeth or to a circular grating line. With these restrictions lifted, it is possible to construct a grating design that exhibits two stigmatic points, points where the focus is free of any aberrations [9], pp. 269-276. The construction method also provides sufficient degrees of freedom that the stigmatic points can be positioned at two of the output waveguides, at the corresponding wavelengths. Also, the design can be adjusted such that the resulting grating line intercepts and reflects most of the light from the input waveguide toward the output waveguides.

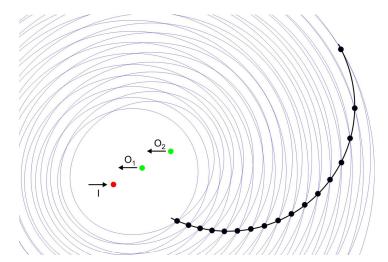

Figure 2: Construction of the grating line for an echelle grating with two stigmatic points.

The design principle is schematically shown in Figure 2. The procedure starts with choosing the positions of the input waveguide (I), and of the two stigmatic points ( $O_1$  and  $O_2$ ). In order to achieve at wavelength  $\lambda_I$  a refocusing onto point  $O_1$ , the reflected contributions from all grating mirrors must arrive in phase at point  $O_1$ . From this requirement we can derive that grating mirror N must lie on an ellipse  $E_{I,N}$  with I and  $O_1$  as focal points. The size of the ellipse is given by the requirement that the path length from I to  $O_1$  via any point on the ellipse is given by  $N \cdot \lambda_I \cdot m/n_{eff}$ , where m is the grating order of the reflection, and  $n_{eff}$  is the effective index of refraction in the free space region. Repeating the above argument for the second stigmatic point  $O_2$ , we find that grating mirror N must also lie on a second ellipse  $E_{2,N}$  with I and  $O_2$  as focal points and a path length from I to  $O_2$  given by  $N \cdot \lambda_2 \cdot m/n_{eff}$ . Combining the two arguments, we arrive at the conclusion that grating mirror N must be placed at the intersection of the two ellipses  $E_{I,N}$  and  $E_{2,N}$ .

# 2.3 Extreme and Conservative layout

Due to the very high index contrast and corresponding small waveguide size for the SOI waveguide technology, the light that leaves the input waveguide will show a very large divergence in the free space region of the echelle grating. This divergence allows designing a very small echelle grating device. However, due to the large divergence it is impossible to capture and reflect all the light from the input waveguide by the grating. This negatively impacts performance twice. First, there are the obvious truncation losses, resulting from capturing only a part of the input light. Second, the part of the input beam that is lost carries the information that describes the higher spatial frequency components of the input spot. Without this part of the beam, the focus of the reflected light can not completely reproduce the input spot and will become broader with a reduced maximum.

The divergence of the light in the free space region can be reduced by widening the input and output waveguides using tapers. In this case a larger angular dispersion is needed to compensate for the increase in distance between the waveguides. This results in a larger grating device, but it is now possible to design a grating that captures virtually all of the input light. This grating can also have more grating teeth, which will improve the device response.

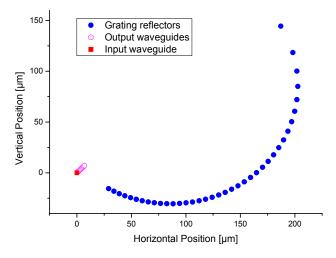

Using both design cases an echelle grating device has been designed. In both designs a 20<sup>th</sup> order grating was used. The "Extreme" layout focuses on minimum size and uses the full divergence resulting from waveguides directly ending in the free space region. This design has 38 grating mirrors and has a total device size of approximately 300 x 200 µm including input and output waveguides. The calculated grating line for this device is shown in Figure 3.

Figure 3: Calculated grating line for the Extreme grating design. In this design, the 500 nm wide waveguides directly end in the free space region, leading to a very strong divergence of the beam in this region.

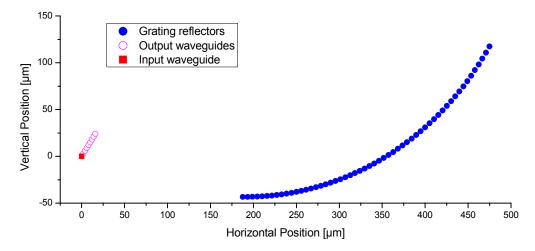

The "Conservative" layout uses tapers to increase mode width at the ends of input and output waveguides to  $2.6 \mu m$ . This device is about twice as large as the "Extreme" device, measuring approximately  $650 \times 170 \mu m$  including input and output waveguides. This device has 55 grating mirrors. The calculated grating line for this device is shown in Figure 4.

Figure 4: Calculated grating line for the Conservative grating design. In this design, the 500 nm wide waveguides are first widened to 2.6 μm before ending in the free space region. The divergence of the beam in the free space region is therefore much lower than for the Extreme design.

## 3. IMPLEMENTATION

#### 3.1 Silicon-On-Insulator waveguide technology

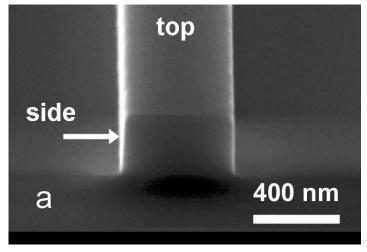

The devices were produced on 200 mm SOI wafers which consist of a silicon substrate with an upper silicon layer of 220 nm thick on top of a 2  $\mu$ m thick buried oxide layer. On these wafers, first a 50 nm thick oxide layer was deposited which will later serve as a hard mask for silicon etching. The wafers were then coated with photo resist and exposed by e-beam lithography. The etching of the wafers was done in a standard 200 mm CMOS line at the IBM Watson Research Center. First the resist pattern was transferred to the oxide hard mask, then the resist removed, and the hard mask pattern used to etch the silicon layer down to the buried oxide. Strip silicon waveguides were defined by etching two parallel wide slots in the silicon layer. The resulting waveguide between the slots has a core cross-section of approximately 500x220 nm and can support a single TE mode in the 1.5  $\mu$ m telecommunications window. An SEM image of such a waveguide is shown in Figure 5. For efficient coupling to a single mode fiber, polymer spot-size converters were added at the in- and out-coupling ends of the input and output waveguides. For more detail on the fabrication process, see References [6], [7] and [8].

Figure 5: SEM image of a Silicon on Insulator strip waveguide, showing the quality of the side-wall facets. Image reproduced from [7].

#### 3.2 Extreme and Conservative layout

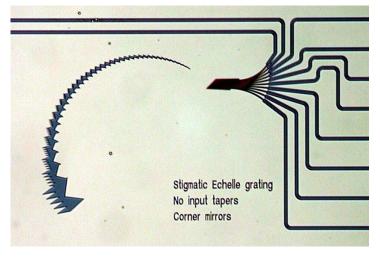

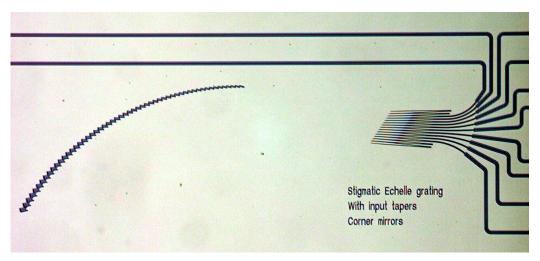

The actual layout of the devices following the Extreme and Conservative grating design are shown in respectively Figure 6 and Figure 7. The dark grey parts of the photographs show the areas where the top silicon layer has been etched away unto the buried oxide layer. The 500 nm wide waveguides are too thin to be visible in these photographs.

Figure 6: Die photograph of an Extreme echelle grating device. Note that the device in the photograph is rotated by 180° relative to the grating line calculation shown in Figure 3.

Figure 7: Die photograph of a Conservative echelle grating device. Note that the device in the photograph is rotated by 180° relative to the grating line calculation shown in Figure 4.

## 3.3 Grating mirrors

For each device type, three different mirror variants were implemented: Flat mirror, Spherical mirror and Corner mirror. Photograph of these three mirror variants are shown in Figure 8. In the devices with flat mirrors, a straight interface between silicon and air is used as a mirror. The Fresnel reflection on this interface reflects only a part of the light resulting in extra losses of about 5 dB. In the device with spherical mirrors, the same type of mirror is used, but in this case the mirror facet is a circle segment with the blaze point as origin of the circle. This design should improve the refocusing of the light from the larger mirrors onto the output waveguides. In the devices with retro-reflecting corner mirrors, the mirror reflection is obtained by reflecting twice under 45 degrees in a corner cube [5]. Theoretically, each facet should reflect 100 % due to total internal reflection, however, because there are two reflections, losses due to facet imperfections will be incurred twice.

Figure 8: Detail photographs showing, from left to right, the "Flat", "Spherical" and "Corner" mirror variants of an Extreme grating device. The light impinges from the top-right onto the mirrors. The jagged lower left edge of each mirror prevents back-reflection of light that has passed through the first interface.

# 4. DEVICE PERFORMANCE

## 4.1 General performance

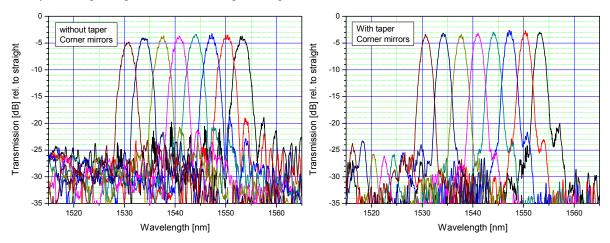

Some examples of responses of echelle grating devices are shown in Figure 9 and Figure 10. These responses are normalized to the transmission of a straight waveguide. Comparing the peak wavelengths of the transmission maxima in the curves, it can be seen that the variation in peak wavelength between different devices on one die is below  $\pm 0.2$  nm, which is very low compared to the channel separation of 3.2 nm, This observation holds even between Extreme and Conservative devices, which have a completely different layout. This result confirms the robustness of the echelle grating devices against local process variations and is an important feature for on-chip telecommunication networks, where many demultiplexing devices on one chip must operate in tune which each other.

Figure 9: Measured response for echelle grating devices using the Extreme design (left) and the Conservative design (right). Both devices use corner mirrors.

## 4.2 Extreme versus Conservative layout

Comparing the responses of two devices using the Extreme and the Conservative layout (See Figure 9), a slightly better transmission can be observed for the Conservative design (3 dB loss), but the difference is small (<0.5 dB) which is unexpected because for the Extreme design extra losses due to reflected field truncation and inferior refocusing of the reflected beam were expected (See paragraph 2.3). The two designs do differ clearly in the width of the transmission peaks, which is 2.4 nm (-3 dB width) for the Extreme layout and only 1.8 nm for the Conservative layout. The Extreme layout shows a more noisy spectral response, limiting the extinction ratio between channels to 16 dB. In the Conservative layout there is less noise and the extinction ratio between channels is 19 dB, limited by side lobes of the transmission peaks. A puzzling feature is the second set of transmission channels, which show up at -25 dB intensity, to the left of the main spectrum in all measurements on Conservative devices. The channel spacing of these channels is reduced with respect to the main spectrum, which suggests that they arise from a reflection of a different grating order. However, the precise origin of this reflection is still unclear.

## 4.3 Comparison of mirror variations

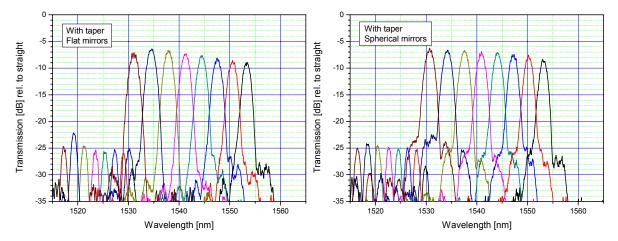

Going from the Corner mirror variant of the Conservative design (Figure 9, right) to the Flat and Spherical mirror variants (Figure 10, left and right), an increase in transmission loss from 3 to approximately 7 dB is visible. Between these variants, the mode of mirror reflection changes from two times total internal reflection in the corner mirror to a single partial Fresnel reflection. Assuming 5 dB loss for the Fresnel reflection, a rough calculation yields a basic loss of 2 dB for all Conservative design devices, and 1 dB (scattering) loss for every mirror facet encountered.

Figure 10: Measured response for Conservative echelle grating devices using flat (left) and spherical (right) mirrors. The response of the Conservative echelle grating using corner mirrors is shown in the previous figure (Figure 9), in the rightmost graph.

## 5. DISCUSSION AND CONCLUSION

The results presented above confirm that the echelle grating design is very robust against process and design variations, and is therefore well suited as a building block for WDM components for on-chip optical networks. This conclusion is further supported by the very small size of the Extreme echelle grating design, which performed almost as well as the much larger Conservative design.

The devices with corner mirrors showed, as expected, clearly lower losses than the devices with flat or spherical Fresnel mirrors. However, given the results, it is well possible that a device with a totally reflecting flat mirror should perform even better. Research on further improvement of the echelle grating devices should therefore focus on alternative flat mirror designs, using e.g. metalized mirrors or mirrors consisting of a Bragg stack.

#### REFERENCES

- F. Xia, M. Rooks, L. Sekaric, and Y. Vlasov, "Ultra-compact high order ring resonator filters using submicron silicon photonic wires for on-chip optical interconnects," Opt. Express 15, 11934-11941 (2007). <a href="http://www.opticsinfobase.org/abstract.cfm?URI=oe-15-19-11934">http://www.opticsinfobase.org/abstract.cfm?URI=oe-15-19-11934</a>

- <sup>[2]</sup> K. Yamada, T. Shoji, T. Tsuchizawa, T. Watanabe, J. Takahashi, and S. Itabashi, "Silicon-wire-based ultra-small lattice filters with wide free spectral range," Opt. Lett. 28, 1663-1665 (2003).

- T. Fukazawa, F. Ohno, and T. Baba, "Very compact arrayed-waveguide grating demultiplexer using Si photonic wire waveguides," Jpn. J. Appl Phys. 43(5B), L673–L675 (2004).

- J. Brouckaert, W. Bogaerts, P. Dumon, D. Van Thourhout, and R. Baets, "Planar Concave Grating Demultiplexer Fabricated on a Nanophotonic Silicon-on-Insulator Platform," J. of Lightw. Technol. 25(5), 1269-1275 (2007).

- Jian-Jun He, Boris Lamontagne, André Delâge, Lynden Erickson, Michael Davies, and Emil S. Koteles, "Monolithic Integrated Wavelength Demultiplexer Based on a Waveguide Rowland Circle Grating in InGaAsP/InP," J. of Lightw. Technol. 16(4), 631-638 (1998).

- [6] S. J. McNab, N. Moll and Yu. A. Vlasov, "Ultra-low loss photonic integrated circuit with membrane-type photonic crystal waveguides," Opt. Express 11, 2927 (2003).

- Y. A. Vlasov and S. J. McNab, "Losses in single-mode silicon-on-insulator strip waveguides and bends," Opt. Express 12, 1622-1631 (2004). http://www.opticsexpress.org/abstract.cfm?URI=OPEX-12-8-1622.

- [8] S. J. McNab, N. Moll, and Y. A. Vlasov, "Ultra-low loss photonic integrated circuit with membrane-type photonic crystal waveguides," Opt. Express 11, 2927-2939 (2003). http://www.opticsexpress.org/abstract.cfm?URI=OPEX-11-22-2927.

- [9] R. März, [Integrated Optics: Design and Modeling], Artech House Inc., Boston & London, 269-276 (1994).